# 12. アセンブリ&パッケージング

## 12-1 スコープ

アセンブリ&パッケージングはシリコンとエレクトロニクスシステムの掛け橋である。アセンブリ&パッケージングは、製品開発において他社に差をつける手段になりつつあることが業界内でますます認識されている。パッケージ設計と組立はシステムアプリケーションにとって重要度が増している。もはや集積回路(IC)の保護だけではなく、今日の製品である民生品からハイエンドのワークステーションに至る範囲で、システムデザイナーが、外観、できばえ、機能を保証させる方法のひとつである。

パッケージングは保護機能以上の性能でなければならない。絶えず増加する性能、高信頼性、熱およびパワーマネジメントを手ごろな価格で提供する要求を満足しなければならない。パッケージング設計のトレードオフは、もはやチップおよびシステムの単独のものではない。それらは副次的な最適化を最小限にするため、システムレベルのアプローチにおけるコンカレント化を考慮しなければならない。パッケージング能力はIC設計や組立に用いられるのと同様に先端的であり、コストパフォーマンスの促進による満足とシリコンとシステムの掛け橋としての要求を満たすように提供されなければならない。チップ機能に対する増加し続ける要求は、チップとパッケージング接続の要件を強調している。インターフェースは不鮮明であり、チップ、パッケージおよびプリント配線板を一体として熟慮することがより重要になりつつある。

アセンブリ&パッケージングの章では、キーチャレンジとプロセス、材料および設計の開発に必要な活動への提言を記載した。成功裏に遂行されれば、パッケージ化された電子製品の競争力の増進に貢献し、それは国際半導体技術ロードマップ(ITRS)のゴールと矛盾がない。

1997 年の出版以来、アセンブリ&パッケージングの章の範囲は拡大されてきた。その内容は、

新しいセクション

システム・オン・ア・チップ(SoC)パッケージング ウェーハレベル・パッケージング フリップチップ・エレクトロマイグレーション

アップデートされたセクション

ミックスドシグナル (アナログ/デジタル混 在 回 路 ) とラジオ周 波 数 (RF) マルチチップ・パッケージング (MCP) シングルチップ・パッケージング (SCP) フリップチップ接 続 (ダイレクトチップアタッチ: DCA) ボンディング/チップ/パッケージ/プリント配 線 板 設 計チップキャリア・サブストレート 熱/電源/グランドマネジメント電気的性能の特徴づけ

バーンインとノウングッドダイ(KGD)は重要なテスト問題で、数チップやマルチチップパッケージングには非常に不可欠なものであるが、この章では説明されていない。横断的な技術要求で、この章で強調されているものとしては次の範囲である。環境、安全&健康、方法論、およびモデリング&シミュレーションである。

多くのアセンブリ&パッケージングロードマップの特質は、エレクトロニクス製品、ボード/サブストレート産業、およびシステムソリューションをもつ多くの挑戦によって推進されてきた。結果として、ある種のパッケージング挑戦はこのロードマップの範囲の外にある。半導体コミュニティの要求と整合し、システム要求のより理解することを保証するために、アセンブリ&パッケージング技術ワーキンググループ(TWG)が続ける努力には、

- TWG 会員は電子システムおよびボード/サブストレート産業からの代表者を含む

- ・ ロードマップ開発の協力機関として、システムはナショナル・エレクトロニクス・マニュファクチャーラーズ・イニシャチブ(NEMI)およびボード/サブストレート産業では、インスティチュート・フォー・インターコネクティング・アンド・パッケージング・エレクトロニクス・サーキット(IPC)である。それぞれのロードマップの範囲は同一である。

- システム、ボード/サブストレートおよびパッケージングロードマップは同期している。

本ロードマップの情報として分類される市場アプリケーションは(以下に示す)、NEMIのロードマップにおける製品部門の定義と矛盾していない。

- ・ ローコスト: < \$300 民生品、マイクロコントローラー、ディスクドライブ、ディスプレイ

- ・ ハンドヘルド: < \$1000 バッテリー駆動製品、移動用製品、ハンドヘルド・セルラー電気通信、その他のハンドヘルド製品

- コストパフォーマンス: < \$3000 ノートブック、デスクトップパーソナルコンピュータ、電気通信</li>

- ・ ハイパフォーマンス: > \$3000 ハイエンドワークステーション、サーバー、航空機、スーパー コンピュータ、最も技術要求の高いもの

- ・ ハーシュ: エンジンルーム、その他の適さない環境

- ・ メモリー: DRAM、SRAM

これらのアプリケーション領域は半導体産業の主力製品の傾向を包含している。本ロードマップで説明されている技術は、それぞれのアプリケーション分野における収益の少なくても80%を提供する(別のことばでは収益比重)ものであるが、ハイパフォーマンスは例外とする。

# 12-2 大チャレンジ

アセンブリ&パッケージング産業が直面する大チャレンジを表7-1に示す。これらの挑戦は、研究コミュニティが最大要求分野に資源の焦点を絞れるようにメカニズムの提供を目指したものである。

| 5 つの大 チャレンジ                          | 問 題 点 のまとめ                                     |

|--------------------------------------|------------------------------------------------|

| ≧100 nm/2005 年まで                     |                                                |

| 高 I/O エリアアレイフリップチップ用 有機 サブストレ        | 鉛フリーはんだ工程と互換性のあるガラス転位点温                        |

| ートの改善                                | 度                                              |

|                                      | 誘電率は2.0に近付く                                    |

|                                      | エリアアレイの低 価 格 での配 線 性 の向 上                      |

|                                      | 低 線 膨 張 係 数 は 6.0 に近 付く                        |

|                                      | 低吸湿率                                           |

|                                      | 高 密 度 サブストレートのテスト                              |

| 高 I/O エリアアレイフリップチップのアンダーフィルの         |                                                |

| 改善                                   | 接 続 接 着 性、低 吸 湿 率、高 密 度 パッドピッチへの               |

| 有機 サブストレートへのフリップチップ実装の信頼性            |                                                |

| 限 界                                  | 自 動 車 用 信 頼 性 は 170℃まで上 昇                      |

|                                      | パッケージングコンポーネントの総合的な要素知識                        |

|                                      | (チップサイズ、アンダーフィル、サブストレート、ヒート                    |

|                                      | シンク、UBM/バンプ)                                   |

|                                      | 物理的設計                                          |

| 理するための設計ツールとシミュレーターの組合わ              | ·                                              |

| せ                                    | 電気的(電力妨害、EMI、高周波時の信号完全                         |

|                                      | 性、低駆動電圧、ミックスド・シグナル相互設計)                        |

|                                      | 商業的 EDA 供給業者の支援                                |

| 銅配線/低比誘電率材料パッケージのシステム信               |                                                |

| 頼性へのインパクト                            | ンダーフィル技術                                       |

|                                      | 誘電体の機械的強度                                      |

| <br> コストパフォーマンスおよびハイパフォーマンス分 野 に     | 境界面の接着力                                        |

| コストハノオーマンスおよいハイハノオーマンス分野における経済的な冷却方法 | 40 C以上の同 囲 温 度 への登 合<br>  チップ内 の電 力 密 度 の局 地 化 |

| 大 チャレンジ                              | ブックNの电力密度の同地化                                  |

| 人 テャレンシ<br><100 nm/2005 年 以 降        |                                                |

| サブストレート技術とチップの隔たりの接近                 | 低損失、低誘電率材料                                     |

|                                      | コスト/ユニット範囲の一定化(コスト/層の減少)                       |

|                                      | 接続密度の尺度はシリコンなみへ                                |

|                                      | 信 頼 性 およびコスト最 適 化 のためのシステムレベル                  |

|                                      | のソリューション                                       |

| 集積回路、パッケージおよびサブストレートのシステ             |                                                |

| ムレベルの観点の要求                           |                                                |

| 高密度デジタルおよびミックスドシグナルパッケージ             | 効果的な設計およびシミュレーション・ツール                          |

| ングの超高周波設計                            | アナログからデジタル設 計ツールへの統 合                          |

| 大型 ボディパッケージの生産性 および信頼性               | サブストレートの平 坦 度                                  |

|                                      | チップからパッケージおよびパッケージからボード間                       |

|                                      | のコプラナリティ                                       |

|                                      |                                                |

# 表 7-2-1 大チャレンジ

\* CTE: Coefficient of thermal expansion(線膨張係数)

\*\* UBM: Under bump metallurgy(アンダーバンプ冶金)

\*\*\* EMI: Electromagnetic interference(電磁妨害)

\*\*\*\* EDA: Electronic design automation(電子的設計自働化)

#### 12-3 技術的要求

パッケージング技術は急速に変化することが続く。アセンブリ&パッケージング要求は、シリコン技術による推進と同様に市場分野要求によっても推進されている。コストは全ての市場分野において技術のトレードオフを推進する。シングル・チップ・パッケージ(SCP)のキーとなる技術要求は国内および国際 TWG で更新されてきており、表 7-3-1 に示す。とはいえアセンブリ&パッケージングコストはコスト/ピンをベースにして全期間を通じて減少することを予測しているが、チップとパッケージのピン数はコスト/ピンの減少よりも急激に増加する。このピン数の急激な増大は、チップ当たりのアセンブリ&パッケージングの絶対コストを増加させるだけでなく、システム当たりのチップ数を削減しない限り、サブストレートおよびシステムレベルのコストを増加させる。ピン数の増加による要求を満足するには、シリコンの生産性をもっと十分なものにテコ入れすることと、産業界は独立したピン数以上の、経済性の高い新規のアセンブリ&パッケージング技術を遂行する必要がある。

# 12-4 パッケージ設計要求

パッケージ設計の複雑さ(チップからモジュールやチップ/モジュールから基板)と対象範囲は、市場が設計サイクルタイムの短縮や高度な設計信頼性を強く要求している。そのかたわら、コストおよび適用性に加えて、物理的、電気的、熱的、機械的、組立性や生産性の考察がパッケージ設計者の前に立ちはだかっている。パッケージ設計プロセスは、設計および分析ツールの絶え間ない改善を要求している。レイアウトや配線および電気的・機械的・熱的設計ツールは、設計サイクルの短縮が実現できれば、使い勝手を高めインターフェースの矛盾性最小限度にするはずである。統合設計システムのゴールは次の 10 年以内である。この統合設計システムの対象範囲には、効果的なチップ/パッケージの相互設計を効果的にするため、チップ設計を含むか、あるいはチップ設計に調和させるべきである。理論的には、これらの要求やトレードオフを実現できるために、パッケージ設計は、システム設計とリンクさせるべきである。

#### 12-5 パッケージ信頼性要求

性能、コストおよび、製品の「軽薄短小」化傾向はパッケージ技術をますます複雑にしていく。その結果的として、新しい材料やパッケージングの形態を採用することになってくる。このパッケージの形態の変化は、新たに信頼性上の危険を伴ってくる。市場サイクルタイムの短縮化と、市場細分化はパッケージ信頼性保証の手順や要求における変化と時間短縮を押し進める。これら新しいパッケージ技術を成功裏に導入するためには、これらの材料の基礎的な物理学的・化学的特性の理解が必要となってくる。つまり、これらの材料が、他のパッケージ材料と信頼できるインターフェースを形成する能力が理解され、結果として生じる不良メカニズムや活性化エネルギーが理解されなければならない。

| 技術 180 nm 130 nm / ード                                                    | 2005              |

|--------------------------------------------------------------------------|-------------------|

|                                                                          | 100 nm            |

|                                                                          |                   |

| コスト(セント/ピン)[A]                                                           | ·                 |

| LC 0.40-0.90 0.38-0.86 0.36-0.81 0.34-0.77 0.33-0.73 0.31-               | -0.70 0.29-0.66   |

| HH 0.50-1.30 0.48-1.24 0.45-1.71 0.43-1.11 0.41-1.06 0.39                | -1.01 $0.37-0.96$ |

| CP 0.90-1.90 0.86-1.81 0.81-1.71 0.77-1.63 0.73-1.55 0.70                | -1.47 0.66-1.40   |

| HP 3.10 2.95 2.80 2.66 2.52 2.                                           | 40 2.28           |

| Harsh 0.50-1.00 0.48-0.95 0.45-0.90 0.43-0.86 0.41-0.81 0.39             | -0.77 $0.37-0.74$ |

|                                                                          | -1.12 0.29-1.01   |

| チップサイズ(・)                                                                | _                 |

|                                                                          | 65                |

|                                                                          | 65                |

|                                                                          | 25 235            |

|                                                                          | 95 622            |

|                                                                          | 65                |

|                                                                          | 67 174            |

| パワー:シングルチップパッケージ(Watts)[B]<br>LC N/A | / A N1 / A        |

|                                                                          | /A N/A<br>.3 2.4  |

|                                                                          | .3 2.4            |

|                                                                          | 50 160            |

|                                                                          | .4 14             |

|                                                                          | .8 2              |

| コアボルテージ(Volts)                                                           | .0 2              |

|                                                                          | .2 1.2            |

|                                                                          | -1.2 0.9-1.2      |

|                                                                          | .2 1.2            |

| HP 1.8 1.8 1.8 1.5 1.5 1                                                 | .2 1.2            |

| Harsh 5.0 3.3 3.3 2.5 2.5 2                                              | .5 2.5            |

| Memory 1.8 1.8 1.5 1.5 1                                                 | .2 1.2            |

| パッケージ・ピン数 [C]                                                            |                   |

| LC 80-290 86-313 90-338 101-365 109-395 118-                             | -426 127-460      |

|                                                                          | -541 203-584      |

|                                                                          | -1247 587-1384    |

| HP[D] 1600 1792 2007 2248 2518 28                                        | 3158              |

| Harsh 40-240 40-259 40-280 40-302 40-327 40-                             | 353 40-381        |

|                                                                          | 160 48-160        |

| パッケージ全体高さ(mm)                                                            |                   |

|                                                                          | .0 1.0            |

|                                                                          | .8 0.8            |

|                                                                          | -1.0 $0.8-1.0$    |

|                                                                          | /A N/A            |

|                                                                          | .0 1.0            |

| Memory   1.2   1.2   1.0   1.0   0                                       | .8 0.8            |

|                                                                          | 70 633            |

|                                                                          | 70 633            |

|                                                                          | 89 1100           |

|                                                                          | 357 2000          |

|                                                                          | 60                |

|                                                                          | /495 150/550      |

| 性能:チップから基板の周辺バス(MHz)                                                     |                   |

|                                                                          | 00 100            |

| HH 75 75 100 100 100 1                                                   | 00 100            |

| CP[F] 133/300 122/330 150/362 150/400 150/445 150,                       | /495 150/550      |

| HP[G] 600 660 727 800 862 93                                             | 28 1000           |

| Harsh 25 40 60 60 60                                                     | 60                |

| Memory[F] | 133/300  | 133/330  | 150/362  | 150/400  | 150/445  | 150/495  | 150/550  |

|-----------|----------|----------|----------|----------|----------|----------|----------|

| 最 大 ジャンク  | ション温度(   | ℃)[H]    |          |          |          |          |          |

| LC        | 125      | 125      | 125      | 125      | 125      | 125      | 125      |

| НН        | 115      | 115      | 115      | 115      | 115      | 115      | 115      |

| СР        | 100      | 95       | 90       | 85       | 85       | 85       | 8 5      |

| HP        | 100      | 95       | 90       | 85       | 85       | 85       | 8 5      |

| Harsh     | 155      | 155      | 155      | 155      | 155      | 155      | 175      |

| Memory    | 100      | 100      | 100      | 100      | 100      | 100      | 100      |

| 最大動作温     | 度:周囲温    | 度(℃)[H]  |          |          |          |          |          |

| LC        | 5 5      | 5 5      | 5 5      | 5 5      | 5 5      | 5 5      | 5 5      |

| НН        | 5 5      | 5 5      | 5 5      | 5 5      | 5 5      | 5 5      | 5 5      |

| СР        | 45       | 45       | 45       | 45       | 45       | 45       | 45       |

| HP        | 45       | 45       | 45       | 45       | 45       | 45       | 45       |

| Harsh     | -40to150 | -40to150 | -40to150 | -40to150 | -40to150 | -40to150 | -40to170 |

| Memory    | 5 5      | 5 5      | 5 5      | 5 5      | 5 5      | 5 5      | 5 5      |

表 7-3-1a アセンブリ&パッケージング技術要求(短中期)

ここで、LC:ローエンド、HH:ハンドヘルド、CP:コストパフォーマンス、HP:ハイパフォーマンス

解決策存在 解決策追究中 解決策未定

|                     |              | 1 0011    | T 0011    |

|---------------------|--------------|-----------|-----------|

| 年                   | 2008         | 2011      | 2014      |

| 技術ノード               | 70 nm        | 50 nm     | 35 nm     |

| コスト(セント/ピン)[A]      |              | •         |           |

| Low Cost            | 0.25-0.57    | 0.22-0.49 | 0.19-0.42 |

| Hand-held           | 0.32-0.82    | 0.27-0.70 | 0.23-0.60 |

| Cost Performance    | 0.57-1.20    | 0.49-1.03 | 0.42-0.88 |

| High Performance    | 1.95         | 1.68      | 1.44      |

| Harsh               | 0.32-0.63    | 0.27-0.54 | 0.23-0.46 |

| Memory              | 0.25 - 0.74  | 0.22-0.54 | 0.19-0.39 |

|                     |              |           |           |

| Low Cost            | 72           | 81        | 90        |

| Hand-held           | 72           | 81        | 90        |

| Cost Performance    | 270          | 308       | 351       |

| High Performance    | 713          | 817       | 937       |

| Harsh               | 72           | 81        | 90        |

| Memory              | 200          | 229       | 262       |

| パワー:シングルチップパッケ      | ージ(Watts)[B] | ·         |           |

| Low Cost            | N/A          | N/A       | N/A       |

| Hand-held           | 2.5          | 2.6       | 2.7       |

| Cost Performance    | 104          | 109       | 115       |

| High Performance    | 170          | 174       | 183       |

| Harsh               | 14           | 14        | 14        |

| Memory              | 2.5          | 3.0       | 3.5       |

| コアボルテージ(Volts)      |              |           | l .       |

| Low Cost            | 0.9          | 0.6       | 0.5-0.6   |

| Hand-held           | 0.6-0.9      | 0.5-0.6   | 0.3-0.6   |

| Cost Performance    | 0.9          | 0.6       | 0.5-0.6   |

| High Performance    | 0.9          | 0.6       | 0.5-0.6   |

| Harsh               | 2.5          | 2.5       | 2.5       |

| Memory              | 0.9          | 0.6-0.9   | 0.5-0.6   |

| パッケージピン数 [C]        |              | <u>I</u>  |           |

| Low Cost            | 160-580      | 201-730   | 254-920   |

| Hand-held           | 256-736      | 322-927   | 406-1167  |

| Cost Performance    | 740-1893     | 932-2589  | 1174-3541 |

| High Performance[D] | 4437         | 6234      | 8758      |

| Harsh               | 40-480       | 40-604    | 40-761    |

| Memory              | 48-182       | 48-200    | 48-220    |

| パッケージ全体高さ(mm)       |          |          |          |

|---------------------|----------|----------|----------|

| Low Cost            | 1.0      | 1.0      | 1.0      |

| Hand-held           | 0.65     | 0.65     | 0.5      |

| Cost Performance    | 0.65-0.8 | 0.65-0.8 | 0.5-0.65 |

| High Performance    | N/A      | N/A      | N/A      |

| Harsh               | 1.0      | 1.0      | 1.0      |

| Memory              | 0.65     | 0.65     | 0.5      |

| 性 能:チップ内(MHz)[E]    |          |          |          |

| Low Cost            | 840      | 1044     | 1250     |

| Hand-held           | 840      | 1044     | 1250     |

| Cost-performance    | 1400     | 1800     | 2200     |

| High-performance    | 2500     | 3000     | 3600     |

| Harsh               | 100      | 100      | 100      |

| Memory(D/SRAM)      | 175/700  | 200/900  | 225/1100 |

| 性能:チップから基板の周        | 辺バス(MHz) |          |          |

| Low cost            | 125      | 125      | 150      |

| Hand-held           | 125      | 125      | 150      |

| Cost-performance[F] | 175/700  | 200/900  | 225/1100 |

| High Performance[G] | 1250     | 1500     | 1800     |

| Harsh               | 100      | 100      | 125      |

| Memory[F]           | 175/700  | 200/900  | 225/1100 |

| 最 大 ジャンクション 温 度 (℃  | )[H]     |          |          |

| Low Cost            | 125      | 125      | 125      |

| Hand-held           | 115      | 115      | 115      |

| Cost Performance    | 85       | 85       | 85       |

| High Performance    | 85       | 85       | 85       |

| Harsh               | 185      | 185      | 185      |

| Memory              | 100      | 100      | 100      |

| 最大動作温度:周囲温度         | (℃)[H]   |          |          |

| Low Cost            | 5 5      | 5 5      | 5 5      |

| Hand-held           | 5 5      | 5 5      | 5 5      |

| Cost Performance    | 45       | 45       | 45       |

| High Performance    | 45       | 45       | 45       |

| Harsh               | -40to180 | -40to180 | -40to180 |

| Memory              | 5 5      | 5 5      | 5 5      |

表 7-3-1b アセンブリ&パッケージング技術的要求(長期)

#### 表 7-3-1a/b の注釈

- [A]全てのコストは、シリコン、ヒートシンク、あるいはテストを含んでいない。サブストレートのコストは、 全体のコストの 30%・50%を超えないものする。

- [B]コスト指向の熱マネジメント問題ののため、コストパフォーマンスは≧65W、ハイパフォーマンスは≧110W で解決策検討中とする。コストパフォーマンスのデータは、デスクトップ分野用である。ノートブック分野は最大14W が1999 年における限界値である。メモリ消費電力(パワー)は SRAM チップのものとする。

- [C]パッケージ/サブストレートのコスト問題を反映している。RAMBUS およびその他の続いて発表されるメモリは除外した。

- [D]ハイパフォーマンスの集積回路は2つの分野に大別できる。特定用途向集積回路(ASIC)は多数の信号端子(ピン)を持つ。電源/グランドのピン総数は信号線の約2分の1である。マイクロプロセッサーの信号端子数は ASIC に比べてもっと少ないが、しかしながらマイクロプロセッサーの電力消費は、ASIC に比べてもっと高い。数多くの電源/グランド端子を持っていながらも、有効的な

全体にわたるインダクタンスは、依然として高い。チップ内(上)へのデカップリング・キャパシタンスが必要である。理論的に、デカップリング・キャパシタンスをチップ内(上)に置きたいのであれば、

$C(de\text{-coupling}) = 9Power/\{f(on\text{-chip}) \times [Core Voltage]\}$

こうした検討は、多くのハイパワー・コストパフォーマンス分野に適応できる。

- [E]>450MHz は改善されたインピーダンスコントロールの必要性を反映したものである。

- [F]xx/yyy は、ハイエンドとコストパフォーマンス分野におけるシステムメモリと周辺バス速度(xx)およびプロセッサのキャッシュメモリへのデータ転送速度(yyy)を言及している。メモリ性能は、プロセッサ・バスの要求に整合すること、およびチップ上の周波数で動作する幅を減少したマルチプレックスド・バスのようなデバイスあるいはアレイレベルの新しいアーキテクチャからの要求にも整合しなければならない。

- [G]>1000MHZ は改善されたインピーダンスコントロールの必要性を反映したものである。

- [H]不確定な材料の解決策。パッケージ/サブストレートのコスト問題を反映。

# 12-6 解決策候補

## 12-6-1 統合設計環境

表 7-6-1-1 は、統合設計環境の解決策候補を示したものである。この解決策の多くは、パッケージ用コンピュータ支援設計システム(CAD)に組み込まれるであろうモデル化・シミュレーション能力を含んでいる。設計ツールは、性能限界まで達しているパッケージの複雑性を管理するために必要とされている。短期的には、これらツールに対する主な焦点としては、フリップチップ/エリアアレイ基板を含むことである。 長期的には、専門家能力を有する統合設計システムがひとつの潜在的解決策である。これらの特徴が、概念から商業的に価値のあるツールへ移行することが要求される機関は著しく短くしなければならない。ツール開発サイクルの加速は、大学と電子自動設計(EDA)供給業者の親密なパートナーシップが求められることになる。 統合設計環境の広い囲な実施は、チップ設計システムが、チップとパッケージの相互設計を許容するチップ設計システムとのインターフェースとなるかもしれない。

| IC 生産の初年度            | 99 | 2002 | 2005 | 2008 | 2011 |  |

|----------------------|----|------|------|------|------|--|

| 物理的設計                |    |      |      |      |      |  |

| 要因牽引 SCP システム        |    |      |      |      |      |  |

| 要 因 牽 引 MCP プレース/ルート |    |      |      |      |      |  |

| 電気的設計                |    |      |      |      |      |  |

| 電 磁 インターフィス/互 換 性    |    |      |      |      |      |  |

| 伝 播 / ノイズシミュレーション    |    |      |      |      |      |  |

| ミックスドシグナル MCP        |    |      |      |      |      |  |

| 全波形解析                |    |      |      |      |      |  |

| 電気/光回路複合             |    |      |      |      |      |  |

| 熱                    |    |      |      |      |      |  |

| 複 雑 系 システム内 気 流      |    |      |      |      |      |  |

| 熱力学                  |    |      |      |      |      |  |

| 接 続 部 物 理 /モデル/データ   |    |      |      |      |      |  |

| モデルベースの不 良メカニズム      |    |      |      |      |      |  |

| インフラストラクチャ           |    |      |      |      |      |  |

| 共通供給業者データ/体制         |    |      |      |      |      |  |

| 自動設計文書               |    |      |      |      |      |  |

| チップ/パッケージ/システム統 合    |    |      |      |      |      |  |

| 電気的                  |    |      |      |      |      |  |

| 電気的熱的/熱力学            |    |      |      |      |      |  |

| トレードオフ/パーショニング・      |    |      |      |      |      |  |

| システム                 |    |      |      |      |      |  |

開発必要 開発中 認定/試作

図 7-6-1-1 統合設計環境解決策候補

#### 12-6-2 サーマルマネジメント

ジャンクション温度を許容範囲内に維持するため、集積回路から熱を放散させる役割は、 半導体およびシステム製造業者にとって重要な挑戦である。電力、ワット数およびジャンクション温度の要求は、表 7-5-1 の市場分類に記載されている。ITRS の予想では、電力の増大とジャンクション温度の低下および経済的な解決策を必要とし続けることから、熱管理挑戦は、今後著しく増加すると指摘している。

ハンドヘルド市場分野では、電力の入手はバッテリー電力限定される。熱放散は、現在ユーザー(ヒートシンクは手や膝)によって限定され、冷却は通常強制冷却なしで成し遂げられる。コミュニケーション(この市場の高性能化と高電力化に牽引される)による演算集中の増加およびシステムレベルでの冷却の必要性の増加(ひとつ以上のホットデバイスの搭載)は、より高いパワーデバイスの使用の要望となり、挑戦は増加する。解決策としては、より高い熱伝導性材料の採用、内部熱抵抗の削減などを含むことができるが、また潜在的には、ユーザーが不満でない範囲内に、もっと新しいアプローチにより冷却を管理することがある。冷却要求は、製品設計における不可欠な部分になってきた。

コストパフォーマンス市場用のデスクトッププロセッサは、システムの強制冷却を必要としており、また電子製品の広い範囲を代表している。エリアアレイフリップチップは、チップの裏面は冷却用の直接放熱パスが用意されている。パッケージングの挑戦は、非常に低い熱抵抗で、経済性が良く、信頼性の高い、なおかつシステムレベルの解決策を可能にさせるチップとの接続を創造することである。システム冷却設計は、この市場においても許容されるもので

あり、コストや、音響上のノイズ、信頼性および大量生産と密接な関係がある。表 7-5-1 で 示したように、目標ジャンクション温度は低下させつつ、電力は増大する。2002 年には、周囲温度との差  $\Delta$  Tは 45 度 C (超過時間は収縮)となる。予想電力 75 ワット(超過時間は長くなる)時は、コストパフォーマンス市場における許容される解決策への重大な挑戦になり、さらに完全性のための、統合された、チップからシステムの解決策の必要を強調する。いくつかのキーとなる開発や革新は、もっと先端的/効率的空気冷却、境界層制御、工学的表面および経済性の高い代替冷却システムである。

ノートブックコンピュータ製品も、コストパフォーマンス市場分野である。バッテリー駆動時において、高い電力レベルを必要としていないにもかかわらず、形状要因、重量および人間工学的問題(ユーザーにとって心地よい外装ケース温度を維持する)に基づいた著しい冷却要求を提出している。ここでの追加開発分野には、内部の熱抵抗の減少工学的表面、新しい新奇性のある冷却システムを含めたものであり、解決策は複数の異なった電力レベルを製品に適用させることである。

ハイパフォーマンス市場分野は、いくつかの異なった世代を通じて劇的な電力の増大を経験してきた。空気冷却は、コストを一定範囲に保っために好んで使われるオプションである。合計チップパワー要求が 100 ワットを超える場合、解決策は電力密度および内部のホットスポットの管理は必要である。理論的なジャンクションおよび周囲温度を仮定すれば、この分野の最大パワーレベルは、コストパフォーマンスの分野におけるジャンクションおよび周囲温度抵抗に比べて 40%から 50%削減することを要求している。現在の解決策は、チップからシステムまでの完全な統合に既に焦点を当てており、このアプローチは続ける必要がある。著しい工学的な開発は、各技術世代での電力増大のために必要であり、クローズドループ冷却システムと同等の能力が必要である。解決策はエンドユースカスタマーの認定がもちろん必要である。主な追加すべき挑戦は、サーマルマネジメントは製品がこの分野からコストパフォーマンス市場分野に移行する路を妨げないことを保証することであろう。

#### 12-6-3 ウェーハバンピング

ウェーハバンピングは ITRS が要求するフリップチップ技術を成功裏に遂行するための鍵となる要素である。有機樹脂サブストレート上の共晶はんだ(錫/鉛)バンプはベンチマーク化された潜在的解決策に対するターゲットを示している。実行され、激増するいくつかの挑戦分野は、コスト、密度、生産性、入手可能性、およびチップ内の銅/低誘電率材料との互換性を包含している。アルファ粒子によって混乱させるソフトエラーを減少する潜在的な解決策は、ローアルファ Pb (鉛) および本ロードマップの期間を通じての鉛フリーはんだへの動きを含めることができる。ウェーハバンピングコスト (アンダーバンプメタル形成 およびバンプデポジションを含め、チップ当たりをベースとした)は、工程単純化により全期間を通じて削減され続けられる必要がある。どんな低いコストの工程でも、信頼性、品質および歩留は維持されなければならない。バンプピッチは、今日の 200  $\mu$  m あるいはそれ以上から、ハイパワー、高 I/O チップは期間の終わりまでに 150  $\mu$  m に縮小されるであろう。このことはサブストレートにおける配線能力を著しく増加させなければならない。ローコストおよびハンドヘルド分野の低 I/O チップは、バンプピッチは表 7-6-4-1 で示されるように、継続して減少する。バンプ形成されたウェーハ

やチップは、パッケージイングされたデバイス以下の価格で一般に入手されるようになるが、品質レベルは同等である。

テストは品質目標への偉大なる技術的挑戦である。テストコンタクターの信頼性は、バンプへのダメージを与ることなく確保されなければならない。フリップチップは、パッケージングされたデバイスと同等であると理解されなければならない。この同等性の達成は短期的な重要課題であり、成功のため産業界の大いなる焦点合わせが必要である。

#### 12-6-4 63錫/37鉛ハンダ製・フリップチップバンプのエレクトロマイグレーション限界

63 錫/37 鉛フリップチップはんだバンプのエレクトロマイグレーション限界にフリップチップ設計ル ールに包含させなければならない。63 錫/37 鉛はんだバンプの平均故障寿命(MTTF: Mean Time To Failure) は、パシベーション・オープニング、平均バンプ温度及び電流の関 数 である。表 7-6-4-1 は、このロードマップの全 期 間 を通じた 10 万 時 間 の平 均 寿 命 達 成 時 のはんだバンプのサイズ要求と推奨するバンプ当たりの最大電流をミリアンペアで示している。 ワイブル分布(確率密度関数)の傾斜は代表的な範囲である4から6を示している。典型的 なフリップチップは多くの電源およびグランドバンプを平行的に持っており、これが実際のデバ イスの信頼性を予言するために計算される必要がある。例として、2005年の100nm世代で、 コストパフォーマンス・マイクロプロセッサは平均電流 80A(1.2 ボルト時 96 ワット)である。150  $\mu$  m のバンプピッチで、パシベーションオープニングが  $65 \mu$  m では、電 流 限 界 はバンプ 温 度 が 80 $^{\circ}$ の時 95mA で、100 $^{\circ}$ のチップ温度では 45mA である。 電源とグランド電流は、チップ動 作 温 度 が 80℃の場 合、各 840 バンプを必 要とし、合 計 1680 バンプが電 流 供 給 用 に必 要 で あり、チップ動作温度が 100  $\mathbb{C}$  の場合、3550 バンプが必要である。 コストパフォーマンスのチ ップは面積 170mm2 で、最大エリアアレイパッドは 7200 バンプであることに注意したい。これ は 2005 年 での限 界 であり、絶 対 に将 来 認 められるものではない。 例として、 2011 年 における 50nm 世代では、コストパフォーマンス・マイクロプロセッサの平均電流は 182A(0.6 ボルト時 109 ワット)で、現 在 の 2.3 倍 である。 このような平 均 電 流 は電 源 とグランドの接 続 に 3820 バン プ(動作温度 80℃)あるいは 8070 バンプ(動作温度 100℃)を必要とする。他のチップから パッケージへの接続解決策として、代替はんだといったようなものを調査する必要がある。

| バンプピッチ  | パシベーション | 各 温 度 における MTTF10万 時 間 達 成 のための |                           |         |  |  |  |

|---------|---------|---------------------------------|---------------------------|---------|--|--|--|

|         | オープニング  | 上 限 電 流                         |                           |         |  |  |  |

|         |         | 100℃                            | 90℃                       | 80℃     |  |  |  |

| 250 μ m | 85 μ m  | 75 m A                          | $110\mathrm{m}\mathrm{A}$ | 165 m A |  |  |  |

| 200 μ m | 80 μ m  | 66 m A                          | 97 m A                    | 145 m A |  |  |  |

| 150 μ m | 65 μ m  | 45 m A                          | 65 m A                    | 95 m A  |  |  |  |

表 7-6-4-1 63 錫/37 鉛フリップチップバンプの電流限界

#### 12-6-5 ウェーハレベル・パッケージング

ウェーハレベル・パッケージングプロセス (WLP) は、IC パッケージングの全でがウェーハレベルで形成されることで、新しい技術のひとつといえる。最初の段階で、WLP 技術は、トータルウェーハコストの IC パッケージングのコストを一定の割合で維持することができる。これが可能なのは、WLP は個々のチップのパッケージングコストを削減できるからである。WLP 技術を定義するためには、チップサイズが後年縮小するとき、全てのパッケージの接続は、引き続きチップ外形以内に位置していなければならない (ファンインの設計でなければならない)。システムの展望から、WLP の制限はどれだけの I/O 数をチップの下に置くことができるか、および基板設計が配線できるかである。WLP技術の最初の市場分野は、低いものから適度な I/O 密度のアプリケーションで、高歩留の DRAM、Flashメモリに代表される。あるいは他の IC で 100以下の合計 I/O で十分なシリコン面積を持つものを企画している。WLP の最大限の利点を可能にするキー技術は、ウェーハレベルのテストとバーン・インの開発である。I/O ピッチが0.5mmと同等もしくは大きい WLP はアンダーフィルを必要とせず、従って、直接顧客の標準表面実装技術 (SMT)プロセスフローを実行することができる。

# 12-6-6 チップから次のレベルへの接続

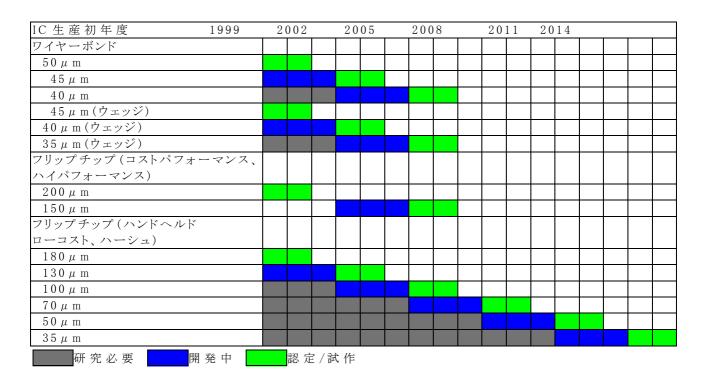

表 7-6-6-1 および表 7-6-6-2 は、チップから次 のレベルへの接 続 の潜 在 的 解 決 策 を示し ている。この表におけるワイヤーボンディングの数値は、インラインのパッドピッチ用でるが、スタ ッガード(千鳥)ボンドパッド構造は、示している数値よりも狭ピッチを実現することができる。フ リップチップ接 続 はパッケージ上 のファンアウト配 線 を必 要とする。 信 号リードは、通 常 外 側 の いくつかの列 に一緒 に置 かれることで、ファンアウトを楽 にするためとパッケージインダクタンス を最小にするために、信号リードは通常多数の電源、グランド線と一緒に外側の数列に配 置される。。エリアアレイの内側の電極部は、IC チップを横切ってチップ上の抵抗に依る電 圧ドロップを最小とするため電源とグランド接続に用いられる。現在のエリアアレイパッドピッチ は 200 μ m で、100 n m 技 術 世 代 と信 号 I/O 数 および電 力 は非 常 に大 きくなるコストパフォー マンスおよびハイパフォーマンス市 場 分 野 では 150μm に縮 小される。 パッドピッチ変 更 は時 としてテストプローブ・ヘッドのコストを最小にするための適用される。この結果は多くの長いフ ァンアウト配 線となる。 平行信 号線間 の過剰 クロストークノイズは、設計段階で注意深く評価 されなければならない。 ハンドヘルド・アプリケーションの中には、チップサイズとチップのパワー (電源)が小さく、コストパフォーマンスおよびハイパフォーマンス市場分野で採用されているも のよりも狭ピッチのエリアアレイが必要となる。これは表 7-6-6-1 の個別の列に示した。低供 給電流アプリケーションでは、異方導電性接着がエリアアレイ接続に用いられるであろう。

| 年                   | 1999    | 2000 | 2001 | 2002    | 2003 | 2004 | 2005             |

|---------------------|---------|------|------|---------|------|------|------------------|

| テクノロジーノード           | 180 n m |      |      | 130 n m |      |      | $100\mathrm{nm}$ |

| チップ接 続 ピッチ (μm)     |         |      |      |         |      |      |                  |

| ワイヤーボンド:ボール         | 50      | 49   | 47   | 45      | 42   | 41   | 40               |

| ワイヤーボンド:ウエッジ        | 45      | 44   | 42   | 40      | 37   | 36   | 35               |

| TAB                 | 50      | 50   | 40   | 40      | 40   | 40   | 30               |

| フリップチップ (エリアアレイ):コス | 200     | 200  | 200  | 200     | 200  | 200  | 150              |

| トパフォーマンス、ハイパフォーマ    |         |      |      |         |      |      |                  |

| ンス                  |         |      |      |         |      |      |                  |

| フリップチップ:ハンドヘルド、ロー   | 180     | 165  | 150  | 130     | 120  | 110  | 100              |

| コスト、ハーシュ            |         |      |      |         |      |      |                  |

表 7-6-6-1a チップから次のレベル接続潜在的解決策・短中期的

| 年                                     | 2008            | 2011            | 2014    |

|---------------------------------------|-----------------|-----------------|---------|

| テクノロジーノード                             | $70\mathrm{nm}$ | $50\mathrm{nm}$ | 3 5 n m |

| チップ接続ピッチ(μm)                          |                 |                 |         |

| ワイヤーボンド:ボール                           | 40              | 40              | 40      |

| ワイヤーボンド:ウエッジ                          | 3 5             | 35              | 3 5     |

| TAB                                   | 30              | 30              | 30      |

| フリップチップ (エリアアレイ):コストパフォーマンス、ハイパフォーマンス | 150             | 150             | 150     |

| フリップチップ:ハンドヘルド、ローコスト、ハーシュ             | 7 0             | 50              | 3 5     |

表 7-6-6-1b チップから次のレベル接続潜在的解決策・長期的

TAB:テープオートメーティッドボンディング

表 7-6-6-2 チップから次のレベル接続解決策候補

表 7-5-1a に示す多ピンと性能要求を満足するために、フリップチップはチップから次レベルへの接続するのための卓越した技術になるであろう。ワイヤボンド技術は、引き続き進化して、フリップチップコストが有利になるまでは、低価格製品の最も有力な接続技術であろう。低 I/O であるが、高周波対応へのフリップチップの採用について、RF パッケージングは後の

セクションで述べる。サイズ、重量および性能が牽引する製品では、I/Oピッチが  $200~\mu$  m またはそれ以下のエリアアレイのフリップチップ接続が必要になろう。この接続アプローチは、必要な性能とコストで入手可能な互換性のあるアンダーフィルとサブストレート技術が必要である。接続の階層はこの技術によって削除することができる。材料、プロセス開発および計測学技術改善は、フリップチップの実施をサポートするためにも必要であろう。エリアアレイピッチ  $\leq 150~\mu$  m のフリップチップ接続技術は、チップ用地の下のサブストレート I/O 密度を逃がすための非常なプレッシャーを与えることになる。サブストレートの再設計は、通常フリップチップ接続をチップ縮小によって適応させることが必要である。

# 12-6-7 エンキャプシュレーションとアンダーフィル

丈夫で低コストのパッケージングの実現と電気的および熱的要求を満足するために、ボールグリッドアレイ(BGA)パッケージには、低コスト、低応力、低粘度で高いガラス転移点のモールディング・コンパウンドが必要となる。チップとサブストレートの線膨張係数(CTE)のミスマッチに対応するために、有機樹脂サブストレート上へのフリップチップ接続には、信頼性の向上、生産性の改善(高速ディスペンス/速硬化)、高接着性、低吸湿性がアンダーフィルに求められる。アンダーフィルの解決策は、サイクルタイムを増加することなく、標準的な表面実装工程と装置に同等のものにすることである。

## 12-7 シングルチップパッケージ

## 12-7-1 ボールグリッドアレイパッケージ

ピン範囲が 200 ピン以上の多くのアプリケーションで、BGA パッケージは潜在的な解決策を 提供 するであろう。多くの BGA は、IC 外周 でのワイヤーボンド接続 を採用 するであろう。BGA へのエリアアレイフリップチップの接続は、多 I/O もしくはハイパワーチップにとされるであろう。 プラスチックボールグリドアレイ(PBGA)では、フリップチップ接 続 における、シリコン IC と有 機 樹脂 サブストレートの CTE の大きな差によって起きる剪断 応力を小さくするために、アンダー フィル用 液 状 エンキャプシュラント(封 止 剤 )を採 用 することが必 要 になろう。 PBGA に封 止さ れたフリップチップの曲がりは、大きなチップサイズで顕著になり、熱冷却パスに影響を与える ことになり得る。IC チップの狭 いパッドピッチとサブストレート上 のプレーティッド・スルーホール (PTH: めっきスルーホール) の比較的 大きなピッチの間隙変換は PBGA パッケージに全体的 に包含される。BGA パッケージ直下のエリアアレイのはんだボールは、サブストレート上の PTH もしくは PTH パッドと同じピッチを持つ。プリント配線板の信号層の数の最小化のためには、 BGA 底面の信号リードは外側の数列に制限されなければならない。 キャビティダウンの BGA では、内側の列は、ICチップとワイヤボンド接続によって使われる。キャビティアップBGAでは、 内側の列は電源とグランド接続用に制限されるか、もしくは使用されない。表 7-7-1 は、はん だボールアレイピッチに関連させ BGA パッケージの潜在的解決策の最大可能ピン数を示し ている。内側の1/3のはんだボール列は、この表におけるピン数の計算から除外した。必要 であれば、これらの内側列はサブストレートを複雑化させることなしに、電源とグランド接続に 用いることができる。

| 年                 | 1999    | 2000 | 2001 | 2002    | 2003 | 2004 | 2005  |  |

|-------------------|---------|------|------|---------|------|------|-------|--|

| テクノロジーノード         | 180 n m |      |      | 130 n m |      |      | 100nm |  |

| BGA はんだボールピッチ(mm) |         |      |      |         |      |      |       |  |

| Low cost          | 1.27    | 1.27 | 1.27 | 1.27    | 1.00 | 1.00 | 1.00  |  |

| Hand-held         | 1.27    | 1.27 | 1.00 | 1.00    | 1.00 | 1.00 | 1.00  |  |

| Cost-performance  | 1.27    | 1.27 | 1.00 | 1.00    | 1.00 | 1.00 | 1.00  |  |

| High-performance  | 1.00    | 0.80 | 0.80 | 0.80    | 0.80 | 0.80 | 0.65  |  |

| Harsh             | 1.27    | 1.27 | 1.27 | 1.27    | 1.00 | 1.00 | 1.00  |  |

| BGA 可能ピン数         |         |      |      |         |      |      |       |  |

| Low cost          | 312     | 312  | 392  | 392     | 420  | 512  | 512   |  |

| Hand-held         | 392     | 420  | 512  | 512     | 512  | 576  | 684   |  |

| Cost-performance  | 840     | 840  | 1012 | 1012    | 1200 | 1352 | 1568  |  |

| High-performance  | 1680    | 1860 | 2112 | 2380    | 2664 | 2964 | 3280  |  |

| Harsh             | 312     | 312  | 392  | 392     | 420  | 512  | 512   |  |

A=整数 (BGA サイズ/ピッチ); R=整数 (A/3); ピン数 = (A-R)×R×4;ボディサイズは直近の JEDEC サイズの端数を切り捨てた。

表 7-7-1a シングルチップパッケージ:BGA・短 中期

| 年                 | 2008            | 2011   | 2014            |

|-------------------|-----------------|--------|-----------------|

| テクノロジーノード         | $70\mathrm{nm}$ | 50 n m | $35\mathrm{nm}$ |

| BGA はんだボールピッチ(mm) |                 |        |                 |

| Low cost          | 1.00            | 0.80   | 0.80            |

| Hand-held         | 0.80            | 0.80   | 0.65            |

| Cost-performance  | 0.80            | 0.80   | 0.65            |

| High-performance  | 0.65            | 0.50   | 0.50            |

| Harsh             | 1.00            | 0.80   | 0.80            |

| BGA 可能ピン数         |                 |        |                 |

| Low cost          | 684             | 800    | 968             |

| Hand-held         | 800             | 968    | 1200            |

| Cost-performance  | 2112            | 2664   | 3612            |

| High-performance  | 3612            | 6844   | 8448*           |

| Harsh             | 684             | 800    | 968             |

A=整数(BGA サイズ/ピッチ); R=整数(A/3); ピン数 $=(A-R)\times R\times 4$ ; ボディサイズは直近の JEDEC サイズの端数を切り捨てた。

\*50mmBGA の I/O 数 の限 界 であり、表  $8\cdot 2$ a の 8758 ピンを満 足させるものではない

表 7-7-1b シングルチップパッケージ:BGA・長 期

# 12-7-2 ファインピッチ BGA/チップスケールパッケージ

ファインピッチ BGA/チップスケールパッケージ(FBGA/CSP)は低重量で小型サイズ要求に対する潜在的な解決策を提供する。これらのパッケージは、チップ自身より僅かに大きいだけでなく、多様性をもった構造と材料の組合わせが利用できる。サイズの範囲は、4から21mmである。21mmのFBGA/CSPは多ピンのアプリケーションに用いられる。表 7-7-2-1は、 $10^{\sim}21$ mmパッケージサイズ、アレイI/Oピッチ、列数に関係させて、周辺端子配置のエリアアレイ FBGA/CSP 解決策の最大可能ピン数を示している。これらのパッケージでは、はんだボールのピッチは、プリント配線板 (PWB)上の PTH の何分の一かである。ファンアウト配線接続は、プリント配線板上の PTH に結びつくことが要求される。ファンアウト要求を最小にするた

めに、エリアアレイ接続の僅かな外周列だけが使用される。 $0.5 \,\mathrm{mm}\,\mathrm{ピッチ}\,\mathrm{FBGA/CSP}\,\mathrm{tk}$ 、プリント配線板上の PTH あるいは中間レベルビアに繋げる I/O 逃げのため、プリント配線板の配線密度にプレッシャーを与えるであろう。列数を4列以上利用する場合では、ビルドアップ層付きのプリント配線板が必要になる。

これらのパッケージは、高性能化、高密度化およびチップの縮小化への潜在的な利点を提供する。チップサイズが縮小する度に FBGA/CSP が最小サイズになるように再設計される使われ方では、この再設計は、そのパッケージが実装されるプリント配線板に対して、相応した再設計を行わせるであろう。

| 年               | 1999    | 2000  | 2001  | 2002    | 2003  | 2004  | 2005  |

|-----------------|---------|-------|-------|---------|-------|-------|-------|

| テクノロジーノード       | 180 n m |       |       | 130 n m |       |       | 100nm |

| FBGA/CSP エリアアレイ | 0.5     | 0.5   | 0.4   | 0.4     | 0.4   | 0.4   | 0.4   |

| ピッチ(mm)         |         |       |       |         |       |       |       |

| FBGA/CSP サイズ    | 10      | 10    | 10    | 10      | 10    | 10    | 10    |

| (mm/サイド)        |         |       |       |         |       |       |       |

| 列 数 /リード数       | 3/192   | 3/192 | 3/252 | 3/252   | 3/252 | 3/252 | 3/252 |

| (1ファンアウト層)      |         |       |       |         |       |       |       |

| 列 数 /リード数       | 4/420   | 4/420 | 4/320 | 4/320   | 4/320 | 4/320 | 5/380 |

| (2 ファンアウト層)     |         |       |       |         |       |       |       |

| FBGA/CSP サイズ    | 21      | 21    | 21    | 21      | 21    | 21    | 2 1   |

| (mm/サイド)        |         |       |       |         |       |       |       |

| 列 数 /リード数       | 3/456   | 3/456 | 3/576 | 3/576   | 3/576 | 3/576 | 3/576 |

| (1ファンアウト層)      |         |       |       |         |       |       |       |

| 列 数 /リード数       | 4/592   | 4/592 | 4/752 | 4/752   | 4/752 | 4/752 | 5/920 |

| (2 ファンアウト層)     |         |       |       |         |       |       |       |

A=整数 (CSP サイズ/ピッチ); R=列数、リード数 =  $(A-R)\times R\times 4$

表 7-7-2-1a シングルチップパッケージ解決策候補:FBGA/CSP 短中期

| 年               | 2008            | 2011            | 2014            |

|-----------------|-----------------|-----------------|-----------------|

| テクノロジーノード       | $70\mathrm{nm}$ | $50\mathrm{nm}$ | $35\mathrm{nm}$ |

| FBGA/CSP エリアアレイ | 0.3             | 0.3             | 0.3             |

| ピッチ(mm)         |                 |                 |                 |

| FBGA/CSP サイズ    | 10              | 10              | 10              |

| (mm/サイド)        |                 |                 |                 |

| 列 数 /リード数       | 3/348           | 3/348           | 3/432           |

| (1ファンアウト層)      |                 |                 |                 |

| 列 数 /リード数       | 5/540           | 6/624           | 6/792           |

| (2 ファンアウト層)     |                 |                 |                 |

| FBGA/CSP サイズ    | 21              | 21              | 21              |

| (mm/サイド)        |                 |                 |                 |

| 列数/リード数         | 3/792           | 3/792           | 3/960           |

| (1ファンアウト層)      |                 |                 |                 |

| 列 数 /リード数       | 5/1280          | 6/1512          | 6/1840          |

| (2 ファンアウト層)     |                 |                 |                 |

A=整数 (CSP サイズ/ピッチ); R=列数、リード数  $=(A-R)\times R\times 4$

表 7-7-2-1b シングルチップパッケー解決策候補:FBGA/CSP 長期

表 7-7-2-2 は、エリアアレイピッチの機能のひとつとしての高分子シングルチップパッケージングの BGA および FBGA/CSP を図解している。

| IC生産初年度             | 1999            | 2 ( | 002 | 20 | 05 | 200 | 8 | 4 | 201 | 1 | 2 | 014 |  |  |

|---------------------|-----------------|-----|-----|----|----|-----|---|---|-----|---|---|-----|--|--|

| BGA はんだボールパッドピッ     | <b>ノチ</b>       |     |     |    |    |     |   |   |     |   |   |     |  |  |

| 1.0 mm              |                 |     |     |    |    |     |   |   |     |   |   |     |  |  |

| 0.80 mm             |                 |     |     |    |    |     |   |   |     |   |   |     |  |  |

| 0.65 mm             |                 |     |     |    |    |     |   |   |     |   |   |     |  |  |

| 0.50 mm             |                 |     |     |    |    |     |   |   |     |   |   |     |  |  |

| FBGA/CSP はんだボールハピッチ | <sup>パ</sup> ッド |     |     |    |    |     |   |   |     |   |   |     |  |  |

| 0.50-0.80 mm        |                 |     |     |    |    |     |   |   |     |   |   |     |  |  |

| 0.40 mm             |                 |     |     |    |    |     |   |   |     |   |   |     |  |  |

| 0.30 mm             |                 |     |     |    |    |     |   |   |     |   |   |     |  |  |

| 0.25 mm             |                 |     |     |    |    |     |   |   |     |   |   |     |  |  |

表 7-7-2-2 BGA、FBGA/CSP 用 PWB 潜在的解決策

\*FBGA パッケージは、PWB PTH ピッチの何分の一かのはんだボールピッチを持っている。 PWB表面上にはファンアウト配線が必要である。

# 12-7-3 高密度パッケージサブストレートおよびプリント配線板 (PWB)

1999 年版のハイパフォーマンス市場分野に対して BGA パッケージを適用するために、PWB は  $1.0 \, \text{mm}$  ピッチの PTH と、BGA パッケージ底面の  $14 \, \text{外周列に対応するための十分 な信号層を併せて持たなければならない。}$

PWB 上の PTH ピッチは、表 7-7-2-1 および表 7-7-2-2 に示された時間と共に縮小しなければならない。1999 年版の FBGA/CSP 解決策に適用するためには、PWB 最表層の金属配線は、最外列 3 列に対応することが求められる。このことは、PWB は表 7-7-3-1 に示した0.5mm ピッチに近接する 2 つのパッドの間を 2 つの信号線を配線する能力を持たなければいけないことを意味する。ビルドアップ層は、表 7-7-2-1 に示した 4 つもしくはそれ以上の列への接続に使用することができよう。

| 年               | 1999    | 2000 | 2001 | 2002    | 2003 | 2004 | 2005  |

|-----------------|---------|------|------|---------|------|------|-------|

| テクノロジーノード       | 180 n m |      |      | 130 n m |      |      | 100nm |

| FBGA/CSP はんだボール | 0.5     | 0.5  | 0.4  | 0.4     | 0.4  | 0.4  | 0.4   |

| パッドピッチ(mm)      |         |      |      |         |      |      |       |

| パッドサイズ (μm)     | 200     | 200  | 160  | 160     | 160  | 160  | 160   |

| ライン 幅 (μm)      | 60      | 60   | 48   | 48      | 48   | 48   | 48    |

| ライン 間 隙 (μ m)   | 60      | 60   | 48   | 48      | 48   | 48   | 48    |

| 接続列数            | 3       | 3    | 3    | 3       | 3    | 3    | 3     |

表 7-7-3-1a BGA,FBGA/CSP 用 PWB サブストレート解決策候補: 短中期

| 年               | 2008   | 2011   | 2014   |

|-----------------|--------|--------|--------|

| テクノロジーノード       | 70 n m | 50 n m | 35 n m |

| FBGA/CSP はんだボール | 0.3    | 0.3    | 0.25   |

| パッドピッチ(mm)      |        |        |        |

| パッドサイズ (μm)     | 120    | 120    | 100    |

| ライン 幅 (μm)      | 36     | 36     | 30     |

| ライン 間 隙 (μ m)   | 36     | 36     | 30     |

| 接 続 列 数         | 3      | 3      | 3      |

表 7-7-3-1b BGA,FBGA/CSP 用 PWB サブストレート解決策候補: 長期

サブストレートの最も切迫した要求は、コストパフォーマンスおよびハイパフォーマンス分野用のフリップチップ解決策との対応性である。表 7-7-3-3は、機能としてのフリップチップパッドピッチ、パッドサイズおよびライン幅/間隙などのサブストレートの鍵となる特徴を示している。最外列のチップパッドを 50%削減すれば、2 つのピッチ距離に3本の信号線を配置することができる。例として、1999年版では、3つの  $42.5~\mu$  m 信号線を中心間距離  $400~\mu$  m の 2 つのパッドの間に配線することができる。この 4 ライン/2 ピッチは、結果的に 2 列 /ファンアウト層の接続と同等、あるいはコストパフォーマンス分野での 4 列 /2 ファンアウト層と同等になる。同様に、5 本の  $27.5~\mu$  m をこれら 2 パッドの間に配線すると、表 7-7-3-3 に記載する 3 列 /ファンアウト層と同等になる。

全ての信号 I/O パッドおよびいくつかの電源 およびグランドパッドは、表 7-7-3-3 に示すように、いくつかの外側列に配置されると推測される。各々のこれら外側列のパッドは、パッケージサブストレート上のトップサイドで、サブストレートのビアあるいは PTH に接続するようファンアウトの再配線が必要となる。次に、ビアあるいは PTH は全体の配線に接続され、仮に数チップパッケージングサブストレートであっても、あるいは下側のはんだボールに配線されるなら、BGA パッケージを構成している。表 7-7-3-3 に示されるリード数は、表 7-5-1 に示されるピン数と同等もしくは大きいが、しかし通常多くは IC 上のパッド数よりは小さいものである。これら追加が必要になった電源およびグランドパッドは、内側の列に配置されており、外側の列にある電源およびグランドパッドに接続される。IC チップサイズがウェーハ生産性に最適なように縮小されれば、サブストレートがチップ縮小に適するように、通常再設計される。

表 7-7-3-3 で説明 するサブストレートは、逃げの配線のみである。 $50\,\mathrm{nm}$  世代用では、多数の外側列数は、 $150\,\mu$  m ピッチで 17 列に達する。このことは、ファンアウト配線の長さが、IC 直下で  $2.55\,\mathrm{mm}$  もしくはそれ以上の長さに達することを意味している。加えて IC の範囲を超えて追加の長さが必要であるが、それでもパッケージサブストレートの範囲内に収まっている。パッケージサブストレート上の 2 つの平行して走るファンアウト配線間のクロストークノイズは、設計段階で注意深く対処しなければならない。

全体配線解決は、「電子接続ナショナル技術ロードマップ: National Technology Roadmap for Electronic Interconnection」(IPC が提供) および「ナショナルエレクトロニクス製造技術ロードマップ: National Electronics Manufacturing Technology Roadmap」 (NEMI が提供) に記載されている。これらの配線幾何技法は、進展しているサブストレート上へのオンチップ配線を支援する程、十分な密度でない。サブストレートのコストは、表 7・2 に示された全体のアセンブリ&パッケージングコスト(セント/ピン)の 30・50%を超えないものと

する。図 7-7-3-2 に将来の高密度サブストレート材料の開発についての可能性のあるプロセスをまとめた。高ガラス転移点(高 Tg)材料は、チップからパッケージへのアセンブリエ程での多数回にわたる高温リフローに対応するために必要である。大形チップには、チップとパッケージ間の CTE (線膨張係数)整合が必要であり、大形パッケージと PWB 間の CTE 整合も望ましい。低誘電率材料は、電気特性要求と整合するために静電容量負荷を低減させる。低誘電正接材料は、RF 分野に必要である。低吸湿率は、パッケージ信頼性を改善する。図 7-7-3-2 は、BGA、ファインピッチ BGA/CSP およびフリップチップ接続に対応性がある高密度サブストレートのピッチ、ライン幅およびライン間隙に関する機能の解決策を図解している。

図 7-7-3-2 高密度サブストレート材料の潜在的開発手順

| 年                     | 1999     | 2000   | 2001  | 2002  | 2003 | 2004 | 2005  |

|-----------------------|----------|--------|-------|-------|------|------|-------|

| テクノロジーノード             | 180 n m  |        |       | 130nm |      |      | 100nm |

| フリップチップ               | 200      | 200    | 200   | 200   | 200  | 200  | 150   |

| パッドピッチ(μm)            |          |        |       |       |      |      |       |

| パッドサイズ (μm)           | 100      | 100    | 100   | 100   | 100  | 100  | 75    |

| チップサイズ(mm/サイド)        |          |        |       |       |      |      |       |

| Cost-performance      | 12       | 12     | 12    | 12    | 12   | 12   | 12    |

| High-performance      | 17       | 17     | 17    | 17    | 17   | 17   | 17    |

| アレイサイズ=チップエッジに沿った     | パッド数     |        |       |       |      |      |       |

| Cost-performance(最大)  | 59       | 59     | 59    | 59    | 59   | 59   | 79    |

| Cost-performance(必要)  | 51       | 56     | 51    | 56    | 53   | 58   | 75    |

| High-performance(最大)  | 84       | 84     | 84    | 84    | 84   | 84   | 112   |

| High-performance(必要)  | 73       | 81     | 79    | 79    | 79   | 81   | 107   |

| 外側列利用数(ファンアウト層決定      | に必要)     |        |       |       |      |      |       |

| Cost-performance      | 4        | 4      | 5     | 5     | 6    | 6    | 5     |

| High-performance      | 6        | 6      | 7     | 8     | 9    | 10   | 8     |

| ファンアウト要求用有効総配線密       | 度 (cm/sq | . cm)  |       |       |      |      |       |

| Cost-performance      | 200      | 200    | 250   | 250   | 300  | 300  | 333   |

| High-performance      | 300      | 300    | 350   | 400   | 450  | 500  | 533   |

| 配 線 サブストレート(≧3のラインを1  | つ削減しア    | たパッドにも | 置き換える | ) *   |      |      |       |

| ライン 幅 (μm)            | 42.5     | 42.5   | 33.0  | 33.0  | 27.0 | 27.0 | 25.0  |

| ライン 間 隙 (μm)          | 43.1     | 43.1   | 33.6  | 33.6  | 27.5 | 27.5 | 25.0  |

| 配 線 サブストレート(≧5 のラインを1 | つ削減し     | たパッドに  | 置き換える | 5)**  |      |      |       |

| ライン 幅 (μm)            | 27.0     | 27.0   | 23.0  | 20.0  | 17.5 | 15.5 | 15.0  |

| ライン 間 隙 (μm)          | 27.5     | 27.5   | 23.1  | 20.0  | 17.7 | 16.0 | 15.0  |

| 接続リード数                |          |        |       |       |      |      |       |

| Cost-performance      | 752      | 832    | 920   | 1020  | 1128 | 1248 | 1400  |

| High-performance      | 1608     | 1800   | 2016  | 2272  | 2520 | 2840 | 3168  |

<sup>\*≧3.5</sup> 列/ファンアウト層

$A= T \nu$  イサイズ、R= 列 数、リード数  $= (A-R) \times R \times 4$ ;ビアピッチ  $\leq$  パッドピッチ

表 7-7-3-3a フリップチップサブストレートトップサイドファンアウト 解決策候補:短中期

<sup>\*\*≥5.5</sup> 列 /ファンアウト層

| 年                     | 2008         | 2011      | 2014  |

|-----------------------|--------------|-----------|-------|

| テクノロジーノード             | 70 nm        | 50 nm     | 35 nm |

| フリップチップ               | 150          | 150       | 150   |

| パッドピッチ(μm)            |              |           |       |

| パッドサイズ (μm)           | 75           | 75        | 75    |

| チップサイズ(mm/サイド)        |              |           |       |

| Cost-performance      | 12           | 12        | 12    |

| High-performance      | 17           | 17        | 17    |

| アレイサイズ = チップエッジに沿った   | パッド数         |           |       |

| Cost-performance(最大)  | 79           | 7 9       | 79    |

| Cost-performance(必要)  | 75           | 7 5       | 78    |

| High-performance(最大)  | 112          | 112       | 112   |

| High-performance(必要)  | 112          | 109       | 111   |

| 外側列利用数(ファンアウト層決定      | に必要)         |           |       |

| Cost-performance      | 7            | 10        | 14    |

| High-performance      | 11           | 17        | 26    |

| ファンアウト要求用有効総配線密       | 度(cm/sq. cm) |           |       |

| Cost-performance      | 467          | 667       | 933   |

| High-performance      | 733          | 1133      | 1733  |

| 配線 サブストレート(≧3のラインを1   | つ削減したパッドに置き  | き換 える)*   |       |

| ライン 幅 (μm)            | 17.0         | 11.5      | 8.0   |

| ライン 間 隙 (μm)          | 17.5         | 12.1      | 8.6   |

| 配 線 サブストレート(≧5 のラインを1 | つ削減したパッドに置っ  | き換 える) ** |       |

| ライン 幅 (μm)            | 10.5         | 6.5       | 4.0   |

| ライン 間 隙 (μ m)         | 10.9         | 7.1       | 4.8   |

| 接続リード数                |              |           |       |

| Cost-performance      | 1904         | 2600      | 3584  |

| High-performance      | 4 4 4 4      | 6256      | 8840  |

<sup>\*≧3.5</sup> 列/ファンアウト層

$A= T \nu$  イサイズ、R= 列 数、リード数  $= (A-R) \times R \times 4$ ;ビアピッチ  $\leq$  パッドピッチ

表 7-7-3-3b フリップチップサブストレートトップサイドファンアウト 解決策候補:長期

<sup>\*\*≥5.5</sup> 列 /ファンアウト層

| IC生産初年度            | 1999 | 20 | 002 |     | 20 | 05 | 200 | 8 | 201 | 1 | 2 | 014 |  |   |

|--------------------|------|----|-----|-----|----|----|-----|---|-----|---|---|-----|--|---|

| ファインピッチ配線板         |      |    |     |     |    |    |     |   |     |   |   |     |  |   |

| ライン 幅 / 間 隙 (μ m)  |      |    |     |     |    |    |     |   |     |   |   |     |  |   |

| 60/60              |      |    |     |     |    |    |     |   |     |   |   |     |  |   |

| 48/48              |      |    |     |     |    |    |     |   |     |   |   |     |  |   |

| 36/36              |      |    |     |     |    |    |     |   |     |   |   |     |  |   |

| 30/30              |      |    |     |     |    |    |     |   |     |   |   |     |  |   |

| コストパフォーマンス用        |      |    |     |     |    |    |     |   |     |   |   |     |  |   |

| フリップチップサブストレート     |      |    |     |     |    |    |     |   |     |   |   |     |  | İ |

| ライン 幅 / 間 隙 ( μ m) |      |    |     |     |    |    |     |   |     |   |   |     |  | İ |

| 42/43              |      |    |     |     |    |    |     |   |     |   |   |     |  |   |

| 33/33              |      |    |     |     |    |    |     |   |     |   |   |     |  |   |

| 27/27              |      |    |     |     |    |    |     |   |     |   |   |     |  |   |

| 25/25              |      |    |     |     |    |    |     |   |     |   |   |     |  |   |

| 17/17              |      |    |     |     |    |    |     |   |     |   |   |     |  |   |

| 11/12              |      |    |     |     |    |    |     |   |     |   |   |     |  |   |

| 8/8                |      |    |     |     |    |    |     |   |     |   |   |     |  |   |

| 研究必要開              | 発中   |    | 認定  | 三/記 | 作作 |    |     |   |     |   |   |     |  |   |

表 7-7-3-4 高密度高分子サブストレート解決策候補

# 12-7-4 システム・オン・チップ・パッケージング

継 続して増 加 する CMOS 密 度 は、ローコストおよびハンドヘルド分 野 における SoC の非 常 に重要な牽引者となっている。例として、リソグラフフィーのフィーチャーサイズが次世代で改 善され、単体のマイクロコントローラー・コアのチップサイズが、パッドピッチおよびパッド数での 制限が発生し、適宜に縮小されないと仮定する。しばしば、コントローラーコアと DSP コアの 組 合 わせは、チップ I/O 数 において、コントローラーもしくは DSP コア単 体 のどちらかのチップ I/O 数より少なく、I/O パッドが制限されているようなチップ領域にも適用することができるであ ろう。 言い方をかえれば、2 つのパッケージのコストは、1 つのコストと同じもしくは安くなり(パッ ケージコストは 2 分の 1 以 下 になる)、占 有されていた PWB 領 域 は削 減される。このことはチ ップ外 の駆 動 回 路と、遅 延 時 間 および消 費 電 力 が、削 減 されることにもなる。 なお、チップ 上 の配線はこれら2つのコア間におけるデーターバンド幅の価値のある増加をもたらし、それによ って性能が向上される。もう1つ以上の技術世代後には、A/D および D/A コンバーターが DSP およびコントローラーコア内 部 へ集 積されることにより、同 様 な恩 恵 がもたらされるであろう。 いくつかのアプリケーションでは、プログラム能力は非常に重要で、それは小型の組込フラッ シュメモリによって達 成されるであろう。 SoC パッケージングにおける主な挑 戦 は、信 号 完 全 性 と検証を整備することである。デカップリング、シールド、良好なグランド接続などの技術は、ア ナログおよびデジタルの混 合 回 路を最 小 サイズのパッケージに収 めるのに必 要 である。SoC 設 計 ではパッケージの初 期 段 階 から目 的とする設 計 エミュレーションと検 証 が必 要 になるだ ろう。 ウェーハプローブおよびパッケージレベルでのテストの複雑さは、設計段階から検討しな ければならない。

いくつかのアプリケーションでは、次世代においてそれが縮小したとしても、チップサイズは I/O パッドの制限を受けない。チップサイズの縮小はチップコストを削減する。2 つのコアの 1 つのチップへの統合は、チップの歩留に影響を与え、全体にわたるチップコストを増加させる。同等もしくは少ない

I/O リードで、2 つのチップを 1 つに置き換えることにより、2 つのパッケージングを行うよりもコストを削減できるであろう。チップにパッケージを加えたコストが増加するか、減少するかは個々のアプリケーションに依存する。しかしながら、チップ外のドライバー遅延や消費電力の削除、プリント配線板の削減、2 つのコア間におけるバンド幅改善の可能性は、性能志向である SoC アプリケーションの採用においては重要な検討課題になってくるであろう。

# 12-7-5 RF およびミックスドシグナルパッケージング

この分野における挑戦は、いくつかの市場セグメントにまたがって使われる、低コストのモバイルおよび高周波帯域の製品にとって重要性を増加しつつある。2.5 GHz 以下の周波数領域においてシリコン IC の性能の増加は、低コストな解決策になるだろう。GaAs と増加する SiGe の IC は高周波分野に採用されるであろう。信号の完全性とコスト問題は、しだいに支配的になってくる。パッケージへのフリップチップ接続とパッシブコンポーネントのパッケージへの組込は、パッケージレベルの性能のために、鍵となる特権的な技術になるだろう。FBGA/CSP のような低インダクタンスおよび高密度パッケージは、従来のセラミックモジュールよりも低コストな解決策として区分けして、設計者が使用するであるう。

設計サイクルタイムの短縮を容認できるレベルにするために、統合されたモデリングとシミュレーションツールが必要となる。前述したように、シングルチップであるラジオにメモリ、プロセッサーおよびミックスドシグナル機能を結合させるように、性能、物理的サイズおよびコストが牽引する統合は、引き続き到達するであろう。早い設計サイクルタイムおよび正確なシミュレーションは、チップおよびパッケージレベルのどちらにもこの統合を可能にさせるものである。パッケージレベルでの、高速テストおよびより高いレベルでのファンクションテストは、また開発挑戦になろう。マイクロエレクトロメカニカル・システム(MEMS)は、フィルター、スイッチ、オシレータおよび他の部品の組立に、2・4年後に採用されるであろう。それらは小型化、少ない挿入口ス、低消費電力、ICとの集積およびバッチ組立における潜在的な低コストなどの利益を提案する。MEMSデバイスの信頼性、潜在的な温度敏感性およびハーメチック/真空パッケージングは、鍵となる開発挑戦である。

#### 12-7-6 マルチチップパッケージ/マルチチップモジュール/システム・イン・パッケージ

MCM の生産量は市場における予想に反して遅れているが、システムハウスがフリップチップバンプ技術を容認するため追跡している。しかしながら、数チップモジュール(2・3 チップ)は量産に入っている。またMCPの定義は拡大されRFおよびミックスドシグナル製品が含まれている。今後数年間に4・5 チップ(それ以上に複雑な)モジュールは普及すると期待されている。MCP はよくシステム・イン・ア・パッケージ(SiP)と呼ばれ、適切な時間で市場へ提供できる。SoCが、技術的および経済的に、適用されるにつれて、製品コストおよびサイズの縮小が実現化されるように、MCP に搭載される IC の数は削減される。

一定の限られた量のため、ハイパフォーマンス製品は、最良のコストと性能のパッケージ解決策を提供する理由から、古典的な(複雑な)MCM をシステム技術の選択として採用する。極当たり前に、高い I/O 数を持つ 10ものロジックおよびメモリチップが、チップ間の信号遅延を最小化するために極近接して設置される。事実、セラミック MCM 上のシステムは、今日採用されているプラスチック MCM 技術に比べて、配線能力を一桁以上大きくすることが要求されている。重要な検討事項は、パッケ

ージングコスト単体ではなく、システム全体のコスト、システム性能要求および CMOS ベースのシステムの信頼性である。というのも今日の MCM 用の極端な高 I/O 用の DCA が利用できることと、将来のプラスチック MCM に期待されてもおり、標準的な冷却技術を通じてジャンクション温度を低減することを可能にするような極小さな領域に全てのシステムを置き換えることができるからである。この能力は、CMOS チップの信頼性を 3・5 倍 に増加させ、CMOS チップの性能を 15%増加させる。より良いシステム信頼性での駆動が、将来において増加することが期待されていることから、システム設計において MCM の採用拡大が結果として生じると期待される。

一般的に、MCP/MCM/SiP は、ローエンド製品ではコスト削減と実装密度向上要求のために進展し、ハイエンド製品では性能と実装密度の向上要求のために進展するであろう。MCP/MCM/SiP を実現していくことと、フリップチップ技術(アンダーフィルのような)を実現していくことを、互いに解決していくように、フリップチップ技術と同様に、MCP/MCM/SiP(数チップ MCPや古典的な MCM に拘らず)が広く普及するだろう。MCP/MCM/SiP のための他の可能な解決策は、1)単純および複雑なMCP/MCM/SiP の性能要求のために配置・配線を容易にする特殊な物理的設計ツール、2)高密度サブストレートおよびメタライゼーション(金属配線:めっきを含む)技術、3)低コストで提供可能なノウン・グッド・ダイである。チップの手直し性およびモジュール試験は、マルチチップモジュールの複雑性の実現を決定づける重要な要素になろう。

#### 12-7-7 信頼性問題

チップ配線におけるアルミニウムの銅への置き換えや、中間レベルの誘電体材料としての SiO2 の置き換えや、ダイレクトチップアタッチの導入や、およびエリアアレイ接続等を含む新素材やパッケージ構成によってもたらされるパッケージングの複雑さにおける要素の複合が増大している。これらの複数の変化は、パッケージ化されたデバイスの信頼性へのリスクの増大を意味している。新素材が導入される前に、材料特性データが提供できることが非常に重要である。

新しいパッケージ設計、材料および技術は、全ての市場分野における信頼できる性能を可能にするとはいえないであろう。市場で使われる条件の知識と連結された不良メカニズムに関連するもっと深い知識は、新しいパッケージ技術を市場にもたらすのに必要となろう。市場分野の区別による環境的予想のガイドラインは、市場ニーズに適応したパッケージ開発を促進させ、供給業者間はもちろん供給業者と顧客の間の矛盾のない信頼性特性を保証することを助ける。不良メカニズムの物理的および熱力学モデルのさらなる研究の重要視は、この傾向を支持するために必要である。

欠陥分離ツール付きのパッケージ/接続技術の共同開発は、技術導入の加速を助けるために必要である。パッケージおよび接続技術の迅速なおよび人工的でない電気的、物理的な欠陥分離のためのツールの概念および開発は重要である。迅速な技術は、材料バルクおよび境界面特性の統計的重要な研究を遂行することに必要である。現在の欠陥分離および解析技術(例として、X線、音響、およびモアレなど)の範囲の開発は、小欠陥画像処理(X線トモグラフィのような)のための新技術の開発とバランスがとれている必要がある。有機化学界面分析技術は、新しい有機材料の導入にともない重要性が増加している。低アルファ材料は、アルファ放射線によるエラーの誘発を低減するために、ITRSの全期間を通じて検討される必要がある。アルファ放射線効果に対する計測技術と標準化は、先端技術プロセスにおけるアルファ感受性予想の増大を支持することには不十分である。

境界面の層間剥離は、引き続き重大な信頼性ハザード(障害地域)であり、チップの大型化および新素材の動向により悪化するであろう。界面接着力に対する標準化方法および受入検査基準が欠落している。環境要因(温度、相対的湿度)はもちろん界面物理の機能(粗さや合成などのような)および化学的(ファンデルワールス力、双極子、共有結合)特性に対する接着強度および分解率を確立するための基礎的な作業が必要である。チップとサブストレート間の線膨張係数ミスマッチは、大形チップパッケージング関連での信頼性問題を軽減するために、削減されなければならない。

新しい静電破壊(ESD)テスト方法および設備は、ピン数の増加と接続ピッチの縮小を理解するためにも必要である。ベアチップおよびパッケージ化されたデバイスのハンドリング解決策の改善は、ESDに関連する信頼性問題を救うであろう。

# 12-8 クロスカット・ニーズ

# 12-8-1 環境、安全性および健康

アセンブリ&パッケージングは、当座のバイヤーおよび最終的消費者へ手渡されるであろう潜在的なリスクや挑戦を検討しなければならない。使用される材料は、障害のないハンドリング、最後の処理およびリサイクリングを可能にしなければならない。というのも大半のアセンブリ&パッケージングは海外に位置し、多数の司法権と規制団体を考慮しなければならない。

| 問題およびチャレンジ       |                                         | 解決策候補                |              |

|------------------|-----------------------------------------|----------------------|--------------|

|                  | 1・5年                                    | 5・10年                | 10・15 年      |

| リード仕上げおよびフリップ    | ESH展望から全体の改善を                           | リード仕上げおよびフリップ        | リード仕上げへの鉛使用の |

| チップはんだバンプ分野の     | 表す代替材料を保証する                             | チップはんだバンプ分野の         | 撤廃           |

| 鉛使用の 20%削減への規    |                                         | 鉛使用の 80%削減           |              |

| 定を受ける圧力          |                                         |                      |              |

| (欧州自動車分野への撤      |                                         |                      |              |

| 廃)               |                                         |                      |              |

|                  |                                         | フリップチップおよびバンプ        |              |

| 1                |                                         | 技術(および他の新パッケ         | る工程の確認と手段    |

|                  | 作業者への潜在的リスクを                            |                      |              |

|                  | 削減するための管理の改善                            |                      |              |

| リスクを表す           |                                         | 証するために、新プロセス開        |              |

|                  |                                         | 発と効果的な望ましくない         |              |

|                  | -Co, -Pb                                | 化学薬品と工程の遮断とと         |              |

|                  |                                         | もに、ESH 保全ペースの継       |              |

|                  |                                         | 続的改善を保証する            |              |

| - All 511-41-    | 114 ) 5 5 7 114 5 7 17 14               | DFESH*ツールの評価         |              |

|                  | ヘリウムおよび他の不活性<br>材料を採用するプロセスへ            |                      |              |

| る Kr-85 の採用撤廃    | M 科を採用するプロセスへ<br>の変更                    |                      |              |

| 記供記さし、の DCII 細胞の | SEMI S2/S8 摘要のアセン                       | CEMI CO/CO O A TOZAV |              |

|                  | SEMI   S2/S8   摘要のアセン<br>  ブリ&パッケージングツー |                      |              |

| 統合の必要性           | ル;結果的に生命への脅威                            |                      |              |

|                  | のリスクとなる欠陥が一点も                           |                      |              |

|                  | ないことを保証する ESH 評                         |                      |              |

|                  | 価ツール                                    |                      |              |

| カドミウムの使用撤廃(防錆    |                                         |                      |              |

| 剤など)             |                                         |                      |              |

| モールディングコンパウンド    | 適当な代替品の発見                               |                      |              |

| 内の不燃剤としての        |                                         |                      |              |

| 三酸化アンチモンの撤廃      |                                         |                      |              |

| 不燃剤としての臭素の撤廃     | 適当な代替品の発見                               |                      |              |

| サブストレート材料としての    |                                         |                      | 適当な代替品の発見    |

| ベリリウムの撤廃         |                                         |                      |              |

| めっきおよび他の工程での     | 全体消費量の 20%削減ま                           | 全体消費量の 50%削減ま        |              |

| 水消費の削減圧力         | での水のリサイクル/再使用                           | での水のリサイクル/再使用        |              |

|                  | の実施                                     | の実施                  |              |

| エネルギー消費の削減圧      | 全体エネルギー消費量の                             |                      |              |

| カ                | 20%削減までのモールドプ                           | 50%削減までのモールドプ        |              |

|                  | レス、炉および他のエネルギ                           |                      |              |

|                  | 一消費設備の効果的な改                             | 一消費設備の効果的な改          |              |

|                  | 善善                                      | 善善                   |              |

|                  |                                         | 全体使用量の 50%削減ま        |              |

| 費削減への圧力          |                                         | でのめっき作業での化学薬         |              |

|                  | 品のリサイクル改善                               | 品のリサイクル改善            | 果的にゼロ排出作業にする |

| モールディングコンパウンド    |                                         | 熱硬化型対熱可塑型プラ          |              |

| 材料の廃棄物最小化        |                                         | スチックのモールディングコ        |              |

|        | ンパウンドへの最適化使用<br>(使用しないトリムマテリアル<br>やランナーの削減) |                                              |

|--------|---------------------------------------------|----------------------------------------------|

| 製品引き取り |                                             | 製造業者あるいは再処理<br>業者の再使用可能な ESH<br>に優しいチップパッケージ |

\*DFESH:ESH のための設計

表 7-8-1-1 アセンブリ&パッケージング ESH ニーズと解決策候補

# 12-8-2 計測技術

## 12-8-2-1 スコープ

アセンブリ&パッケージングは、将来の電子システムでのサイズ、性能およびコストにおける重要かつ増大する役割を引き続き担うであろう。このセクションはアセンブリ&パッケージングに関連した計測技術挑戦をまとめたものである。これは網羅的なまとめではないが、興味を持つ中で最も重要な領域に重点を置くよう心掛けた。

## 12-8-2-2 現在の技術状況と将来のニーズ

| アセンブリ&パッケージング計測学ニーズ         | 問題点のまとめ                         |

|-----------------------------|---------------------------------|

| チップ、パッケージおよびシステム用の電気的モデリング  | 処理時間と入力準備の効率(結果は分単位、日単位で        |

| とシミュレーションのコーディネート           | はない)                            |

|                             | 放射ノイズを含む効率的なノイズモデリングとシミュレーシ     |

|                             | ョン                              |

|                             | ミックスド RLCG アクティブデバイス周波数ドメインモデル  |

|                             | を活用した SPICE 互換性タイムドメインシミュレーション能 |

|                             | カ                               |

|                             | 要素価値あるいは周波数ドメインモデルおよび2次ネット      |

|                             | ワークあるいはオーダー削減のどちらかの開方をさせるシ      |

|                             | ミュレーション効率モデリングアルゴリズムおよび技術       |

|                             | タイムドメインシミュレータにおける「スタンプ」のように実例   |

|                             | をあげて証明するモデルを作成する効果的全波長分析        |

|                             | 技術                              |

|                             | 電気的、熱的およびコストモデリングの統合とシミュレーシ     |

|                             | ョンツール                           |

|                             | 製造工程の認定、製品ライフタイムの改善および製品の       |

| 明の改善                        | 成功的な操作のための加速ストレス試験技術のモデリン       |

|                             | グおよびシミュレーションの必要性                |

| 界面(界面の理解によって推進される熱性能、信頼性、   | 界面結合強度のためのモデル、設計および基礎的メカ        |

| 歩留およびコスト) のモデリングおよびシミュレーション | ニズム(物理的、化学的、機械的)の制御の必要性         |

| パッケージおよびアセンブリの熱的、機械的シミュレーショ | 材料の現実寿命データによって支持される総合的な熱        |

| ンモデル                        | および機械的モデルツール                    |

| 材料パラメーター                    | 関係するサイズ、厚み、熱用のパッケージング材料の材       |

|                             | 料特性の計測、収集および普及                  |

| 材料アプリケーションおよび組立工程管理         | パッケージおよびバンプチップにおけるはんだシステム、      |

|                             | はんだ代替物、アンダーフィル、封止樹脂、付属材料の       |

|                             | オンライン計測の改善                      |

表 7-8-2-2-1 アセンブリ&パッケージング・モデリングおよび計測技術

クロスカット課題

#### 12-8-3 モデリングおよびシミュレーション

アセンブリ&パッケージング技術は、性能、パワー、ジャンクションおよびパッケージ幾何(パターンなどの配置)の領域の非常に強い要求と一斉に整合するように推進される。したがって、先端的なモデリングツールは、電気的、熱的および機械的見地をカバーすることが必要である。

これらの現象は、もはや個別に記述することができない。自己矛盾のない解決策およびチップ設計ソフトウエアとの統合あるいはコーディネートを実現するための、個別のツールおよびそれらの統合における、より重要な進歩が必要である。チップから基板へのスピードが3GHzへ移行すると、電気信号の伝播モデリング、ノイズおよび放射は、コンピュータ使用(動作時間)および入力効率、現実的な複雑さをアドレスする能力において、形状および配線密度の全ての面からの本質的な改善が必要となる。機械的ストレスは、チップ、パッケージ間の結合のために必要である。低温導電率を持つ低κ誘電体の導入は、より高いパワー放散レベルがもたらす電気的作用の首尾一貫とした解決の必要がある、正確な熱的シミュレーションの必要性を増加させるであろう。

#### 12-8-3-1 パッケージおよびシステムの電気的シミュレーションモデル

チップが個別にパッケージされたシステムあるいはシングルまたはマルチチップパッケージへの集団における電気的作用のモデリングは、実在しているクロック周波数においてさえ、コストおよび時間の効率的な方法において何がなされるかという実際的な制限に陥れている。モデリングおよびシミュレーション技術のより高いクロック周波数とより高密度への拡大は、有益な設計能力の提供を行うために、かなりの研究を行うことを要求することになろう。他の削減技術、タイムドメインあるいは周波数ドメインのどちらか一方、は使用に適した操作時間の実現のために必要になろう。全周波数シミュレーションツールは、ある種の複雑な構造を処理するために必要になろうし、またそれはコンピュータ使用の効率を上げなければならない。パッケージ、チップレベルの設計およびシュミレーションシステムの統合あるいはインターフェースは、接続配置(チップ上あるいはサブストレート上)発生のオプションのような必要性があろう。集積されたチップ、電気的(アーキテクチャ)、機械的、熱的およびコストのモデリングツールは、統合設計および製造チームにとって、サイクルタイム削減の潜在性を持つ、有益なツールになろう。

#### 12-8-3-2 パッケージおよびアセンブルの熱 的 および機 械 的 シミュレーションモデル

業界は引き続き熱放散性、ジャンクション温度および信頼性の増大を予測しており、電子製品の冷却および機械的強度限界を駆り立てている。物理的計測に関連した「実際寿命」の素材データに完全に支援される、熱的および機械的モデルツールのさらなる統合化が必要である。例には、エアーフロー特性の流体および固体モデル、加速試験およびパワーサイクルにおけるストレス予知、インターフェース破面作用のマイクロモデル、振動および機械的衝撃を含むパッケージ力学のマクロ構造モデルが含まれる。これらのモデル方法はまた、接着/アンダーフィルフローや BGA 手直しのような生産および組立工程に適用される。製造工程内特性、ロケーションおよび欠点と欠陥の特性用の計測における、より良い経験的な能力が求められている。鍵となるのは、マイクロモイヤー、ナノ圧痕技術およびインターフェース破面靭性技術などの製造工程内モデルメカニズムの解明と確認モデルの開発である。

## 12-8-3-3 インターフェースの計測 およびモデリング

アセンブリ&パッケージングの熱的特性、信頼性歩留およびコストは、インターフェースの組合わせおよび特性を表す能力、制御およびそれらの強みの理解により推進される。正確な認定能力およびおそらくインターフェース性能の設計と制御は、将来の経済性開発および製造にとって非常に重要なものとして残るであろう。鍵となるのは、金属/高分子、高分子/高分子および金属/無機誘電材料間のインターフェース結合強度(接着力)はもちろん、製造工程を通じたこれらの界面における極めて低いレベルの複合有機物の定量的認定のために、基本的メカニズム(物理的、化学的、機械的)の十分な特性を表すことである。この理解は、インターフェースの完全性の改善にとって極めて重要となろう。