# 超省電力データ処理を実現するハードウェアとアーキテクチャ

国立研究開発法人 產業技術総合研究所 情報技術研究部門 田中 良夫

## はじめに

- 本日の講演では、産総研STAR事業「高電力効率大規模データ処理 イニシアチブ」の成果を中心にお話しさせて頂きます。

- 個別研究課題の詳細については、6月20日に開催された産総研 STARシンポジウム「超省電力データ処理ハードウェアの新潮流と 将来像」のホームページから講演資料が公開されておりますので、 そちらをご参照頂ければと思います。

- https://unit.aist.go.jp/eleman/info/impulse/

- 本日のスライドの多くは以下の方々からご提供頂いています。

- 安田哲二 (産総研ナノエレクトロニクス研究部門長)

- 高野了成(産総研情報技術研究部門サイバーフィジカルクラウド研究グループ長)

- 産総研工レクトロニクス・製造領域研究企画室

- 今日の話は、「省エネ」に限ったものではありません。

- 今後次々開発されるであろう(例えば人工知能向け)ハードウェアをインクリメンタルに導入していくための技術でもあります。

## 発表の流れ

- 問題意識とIMPULSの概要

- フローセントリックコンピューティン

- ポストムーア時代に向けたデータセンター アーキテクチャ

- 2030年に向けた課題の整理とまとめ

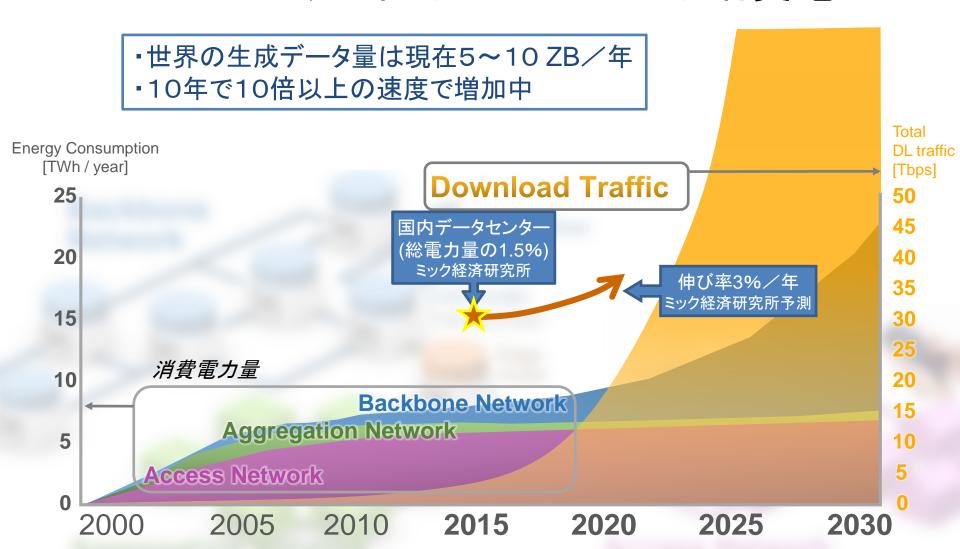

#### インターネットトラフィックとネットワーク消費電力量

K. Ishii (AIST) et al, J. Lightwave technol. V33, N21, Nov. 2015.

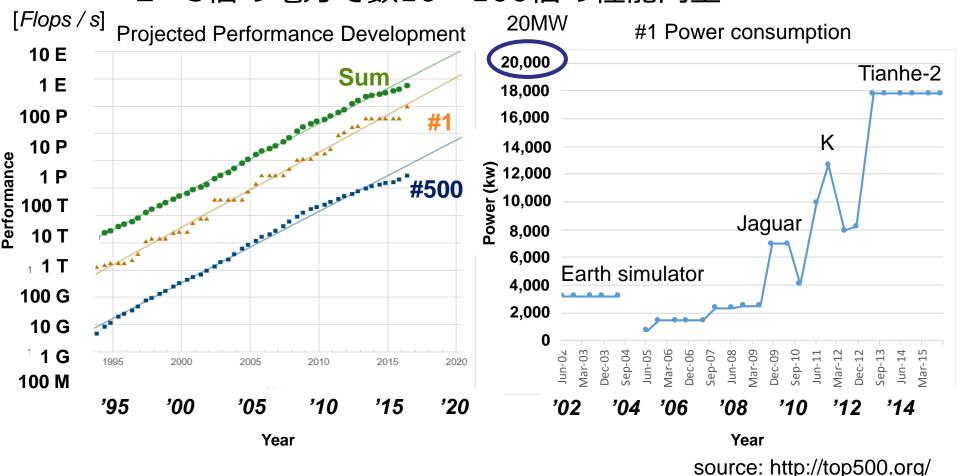

#### スーパーコンピューターの性能と消費電力

- 電力の壁(Power Wall)問題

- 2~3倍の電力で数10~100倍の性能向上

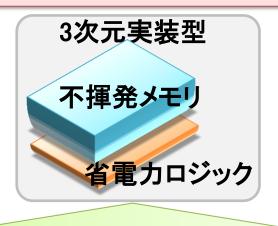

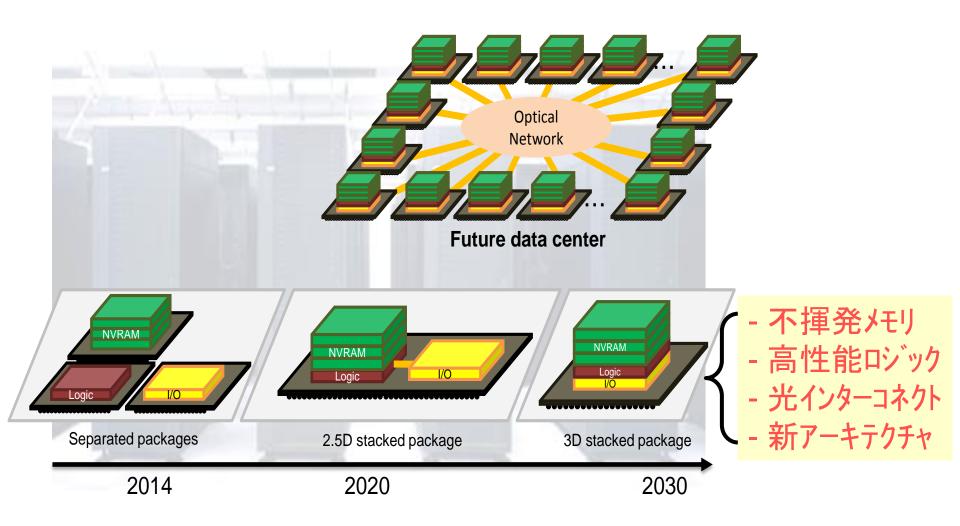

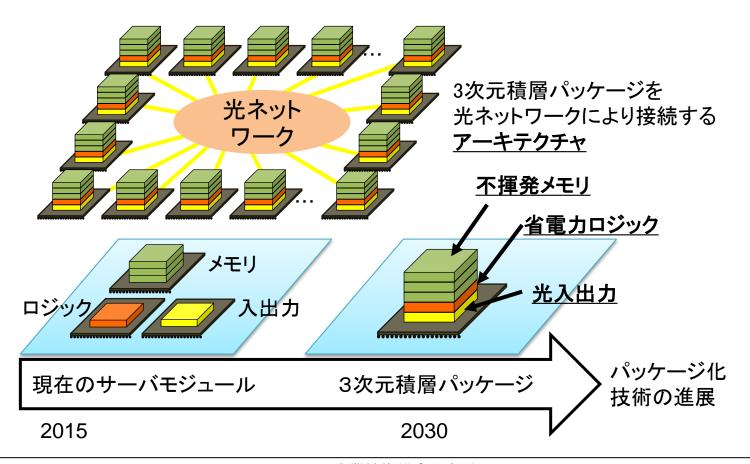

### 将来のデータセンターを構成する要素技術

#### 超集中型データ処理のためのアーキテクチャ

不揮発メモリと ロジックを実装した 高性能モジュール

光ネットワーク

光ネットワークによる 省電力・大容量通信

ストレージクラスメモリ(不揮発メモリ)

HDDストレージ

不揮発メモリによる省エネ・ストレージ

#### IMPULSEが描くデータセンターの将来像

## データ処理の電力効率を100倍以上に

#### シンポジウムのプログラム(産総研からの報告)

- フローセントリックコンピューティング(高野了成)

- 超高集積・超広帯域光ネットワーク(並木周)

- 三次元集積に向けたGeトランジスタ(遠藤和彦)

- 電圧制御スピンRAM(野崎隆行)

- 超省電力トポロジカルRAM(富永淳二)

- 強誘電抵抗変化RAM(澤彰仁)

- 計算シミュレーションによるデバイス材料設計(浅井美博)

- 自動微分を搭載したTCADとその応用(福田浩一、池上努)

- 2030年に向けた課題整理(安田哲二)

## 発表の流れ

- 問題意識とIMPULSの概要

- フローセントリックコンピューティン

- ポストムーア時代に向けたデータセンター アーキテクチャ

- 2030年に向けた課題の整理とまとめ

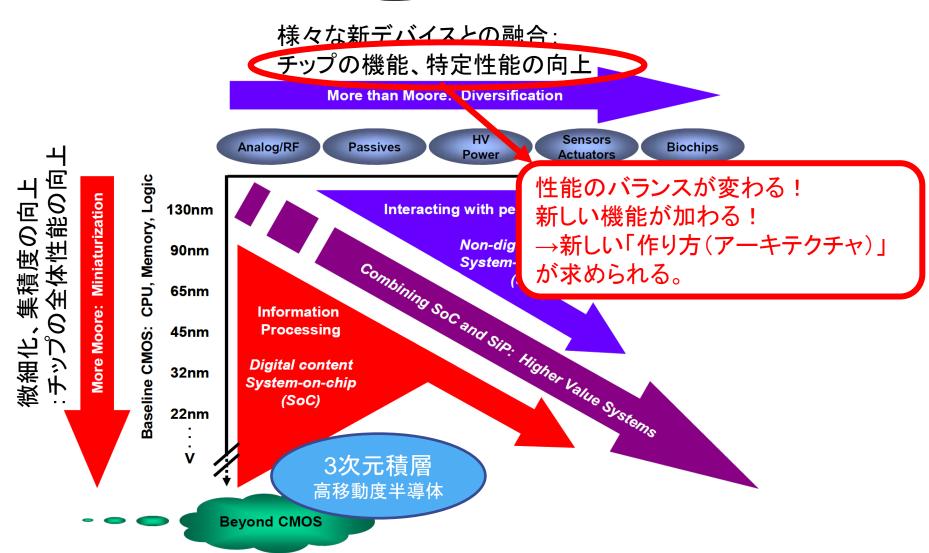

## More MooreとMore than Moore

Source: Fig.3 of "More-than-Moore White Paper," ITRS white paper, 2010

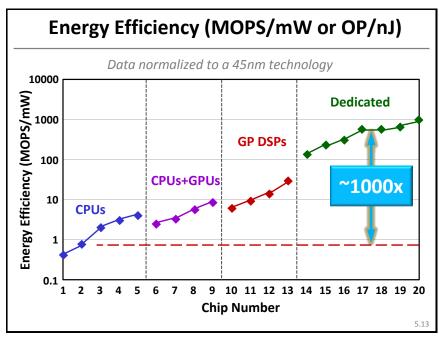

## ポストムーア時代の計算機

- 専用回路が陳腐化しない

- 深層学習用チップ

- イジングマシン

- ニューロチップ

- 2次元から3次元へ

- CMOS積層、TSV

- メモリの大容量化・ 広帯域化

- 光通信によるIOの広帯域化

Markovic@UCLA

## 省電力を意識したデータ処理

今後の計算機はBYTE/FLOP比が一転増加するように進化(「FLOPSからBYTE中心へ」by 松岡先生@東工大)

- ・データ移動のコスト大

- ①データを極力動かさないで処理

- データ移動のコスト小

- ②計算を再利用

- ③専用エンジンにデータ移動して処理

使い分け が必要

## ポストムーア時代の計算パラダイム

- 省電力かつ高速データ移動が可能になれば、

- 現在:データのある場所で計算

- 提案:機能がある場所にデータを移動

**Data affinity Processing**

moving computation to data

**Function affinity Processing**

moving data to computation

heterogeneous task specific processors

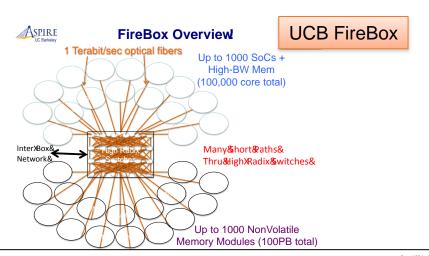

## 将来のデータセンタアーキテクチャ

専用プロセッサやメモリ、ストレージを光ネットワークで 接続する包括的な計算機システムアーキテクチャが必要

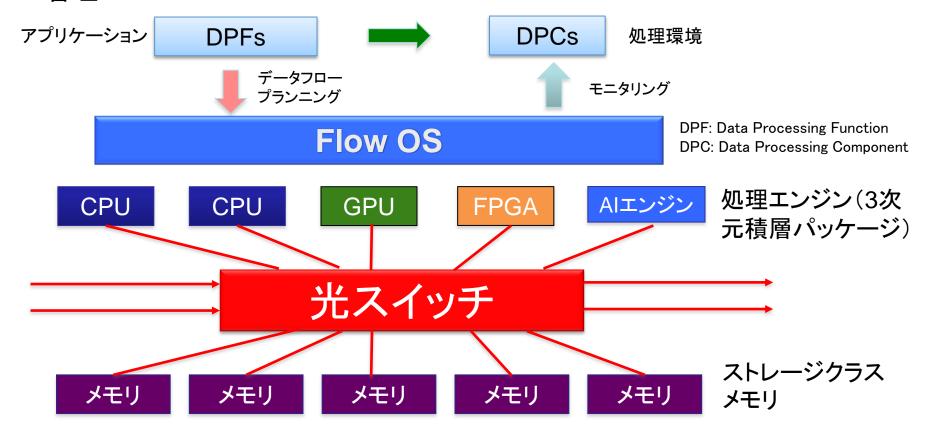

#### フローセントリックコンピューティングの提案

- レゴブロックのようにアプリケーション毎に必要な部品(処理エンジン、ストレージクラスメモリ)を適材適所で組み合わせたシステム構成を動的に構築

- データセンタ全体を一つのオペレーティングシステム(OS)で効率的に運用・ 管理

## 関連プロジェクト

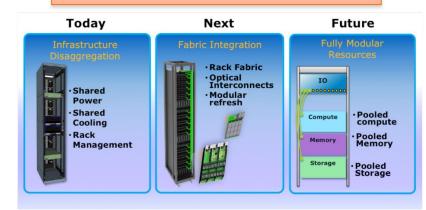

- 従来型アーキテクチャ

- All-in-oneサーバの集合→性能面、 管理コスト面でスケールしない

- ディスアグリゲーテッド・アーキテクチャ

- 各機能ブロックを分離(ディスアグリ ゲート)し、それぞれを広帯域光インタ コネクトで接続

- 用途に応じて構成を動的に再構成

- コンセプト先行で、技術は未開発

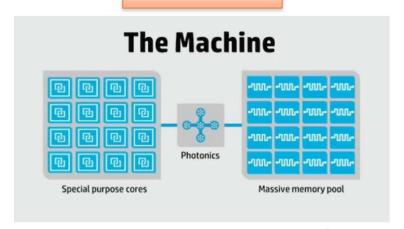

#### Intel Rack Scale Architecture (RSA)

**HP The Machine**

用途特化型コア + フォトニクス + ユニバーサル (SoC) (+ファブリック) メモリプール

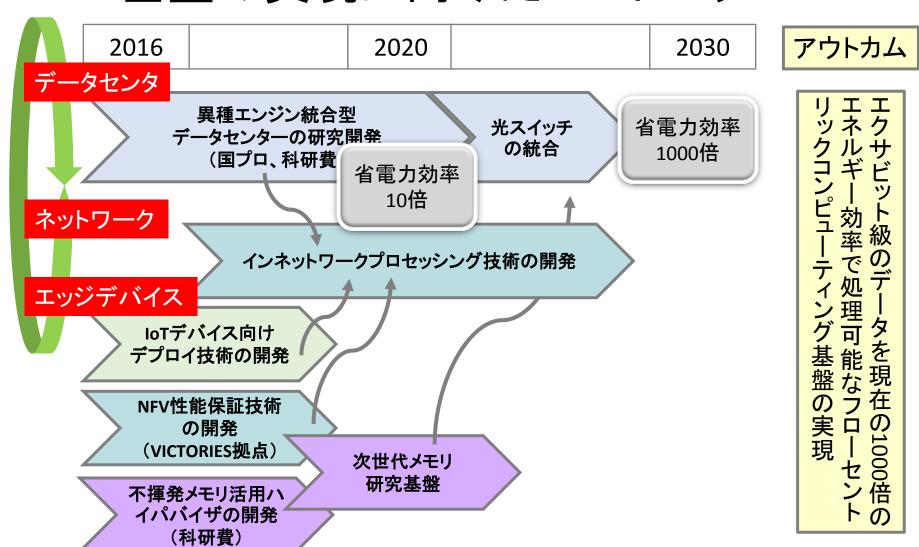

## フローセントリックコンピューティング 基盤の実現に向けたロードマップ

## 常に進化するシステムソフトウェア

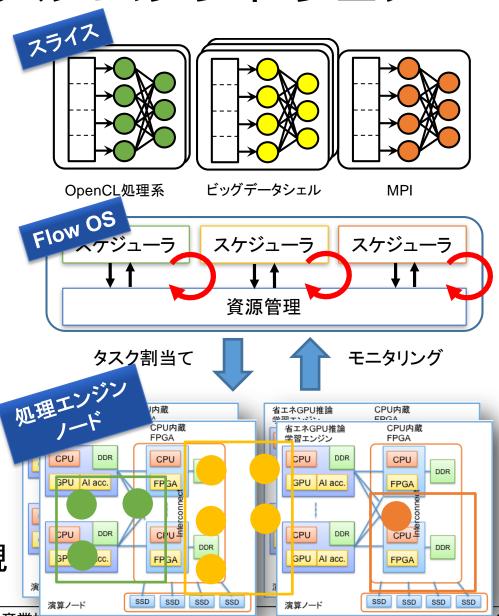

#### クラウド資源管理システム (Flow OS)

- アプリの実行に必要な処理エンジンを適材適所に組み合わせた実行環境(スライス)を提供

- 階層的スケジューリングと 分散モニタリングにより、 スライス毎に最適な資源 割当てを調整

- 動作履歴の時系列学習により資源割当てが賢くなる 進化型スケジューラを実現

## 発表の流れ

- 問題意識とIMPULSの概要

- フローセントリックコンピューティン

- ポストムーア時代に向けたデータセンター アーキテクチャ

- 2030年に向けた課題の整理とまとめ

## シンポジウムでご報告した成果と課題のまとめ

| 要素技術        | プロジェクト成果                                                                        | 今後の技術課題                                                                                         |

|-------------|---------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|

| アーキテクチャ     | <ul><li>フローセントリックシステムの提案</li><li>NV-RAMを活用した仮想化</li><li>実行環境最適化OSコンテナ</li></ul> | <ul><li>システムレベル概念実証</li></ul>                                                                   |

| 光ネットワーク     | • 大規模光スイッチ、合分波器、<br>波長可変フィルタ実証                                                  | <ul><li>波長多重トランシーバ実証</li></ul>                                                                  |

| ロジック        | <ul><li>三次元化に適したGe CMOS<br/>プロセス</li></ul>                                      | <ul><li>三次元ロジック設計、チップ<br/>実証</li></ul>                                                          |

| 不揮発メモリ      | ・ 電圧制御・電界アシストによる低電力動作にメド                                                        | <ul><li>スケーリング実証(&lt;10nm)</li><li>エラー率(スピンRAM)、<br/>書換え耐性(相変化RAM)、<br/>データ保持(強誘電RAM)</li></ul> |

| 設計・シミュレーション | <ul><li>第一原理計算からのデバイスシミュレーション</li><li>自動微分を装備したTCADプロト完成</li></ul>              | <ul><li>マルチスケールシミュレー<br/>ションの確立</li><li>大規模設計・解析への適用</li></ul>                                  |

## 国プロへの展開、企業連携の状況

アーキテクチャ

ロジック

光ネットワーク

不揮発メモリ

シミュレーション

国プロ提案中

2015~ 産総研コンソ PHOENICS 活動中

ImPACT・無充電で長期間使用できる 究極のエコIT機器の実現

CREST・二次元機能性原子・分子薄膜の創製と利用に資する基盤技術の創出

NEDO·超先端材料超高速開発基盤技術Pi

拠点整備

NEDO・IoTオープンイノヘーション推進事業

## 超省電力なデータ集中処理実現のシナリオを創る

課題:要素技術の強みを、システム化・ビジネス化に結びつける

アーキテクチャ

・世界最速スパコンで培った システム化技術

光ネットワーク

- ・光通信関連企業群の存在

- ・世界水準のシリコンフォトニクス

ロジック

- ・省電力チップの設計技術

- 微細化終焉後のトランジスタ 技術

不揮発メモリ

- ・最先端フラッシュ国内生産

- \*新原理RAM開発で世界をリード

グローバルなエコシステム

ITサービスから材料・装置まで 幅広いレイヤーの知識と技術を統合

### まとめと提案

- ポストムーアに向けて、超省電力かつ高効率な次世代データセンターアーキテクチャとフローセントリックコンピューティングの概念を紹介。

- デバイスを含めた研究開発については、国際ロードマップ(IRDS) とこれに対応した国内の検討体制の準備が進行中。その対象は 幅広く、検討結果は公開。

- 波及効果の大きい超高効率データセンタにフォーカスして、技術開発とビジネス化の総合的な戦略を描くことが重要。これを産総研が中心となって進めていきたい。

- ✓ コンソーシアム設立を検討中(参加企業は国内に限らない)。

- ✓ 共同開発やプロジェクト提案を主導。

- ✓ 幅広い技術レイヤーにわたるグローバルなエコシステムへ。

- ご関心ある方は産総研ナノエレクトロニクス研究部門長安田哲ニ (<u>yasuda-t@aist.go.jp</u>)までご一報を。