1000

### Standard of Electronic Industries Association of Japan

# **EIAJ ED-5515**

# Stub Series Terminated Logic for 2.5Volts (SSTL\_2) Differential Input Signal Specifications

Established in September, 1998

Prepared by

Technical Standardization Committee on Semiconductor Devices

Published by Electronic Industries Association of Japan

5-13, Nishi-shinbashi 1-chome, Minato-ku, Tokyo 105-0003, Japan Printed in Japan

#### Standard of Electronic Industries Association of Japan

# Stub Series Terminated Logic for 2.5 Volts (SSTL\_2) Differential Input Signal Specifications

#### 1. Scope

This standard defines the differential input signal specifications for high frequency operation of Stub Series Terminated Logic for 2.5V (SSTL\_2), previously standardized as EIAJ standard (EIAJ ED-5513).

Thus, the standard conforms to SSTL\_2 standard and additionally defines differential input signal specification for high frequency operation devices.

#### 2. Standard Structure

The standard is defined in three sections;

The first section defines values of input signal parameters which is used to test differential input signal specifications. The second section defines test conditions to perform differential AC input test.

Further more, in the third section describes, as reference only information, typical example of SSTL\_2 class I differential input circuit, and SSTL\_2 clock input circuit using direct termination resister. Also, for the SSTL\_2 clock input circuit using direct termination resister, offset voltage parameter Viso and Viso deviation parameter  $\triangle$ Viso are mentioned as reference only parameters.

#### 1.0 Differential input parameters

Table 1.0-a Differential input DC logic levels

| Symbol                     | Parameter                     | Min.  | Max.                   | Units Notes |     |

|----------------------------|-------------------------------|-------|------------------------|-------------|-----|

| V <sub>IN</sub> (DC)       | DC input signal voltage       | -0.30 | $V_{DDQ} + 0.30$       | V           | · 1 |

| V <sub>SWING</sub><br>(DC) | DC differential input voltage | 0.36  | V <sub>000</sub> +0.60 | V           | 2 . |

#### <Notes>

- 1.  $V_{IN}$  (DC) specifies the allowable DC execution of each differential input.

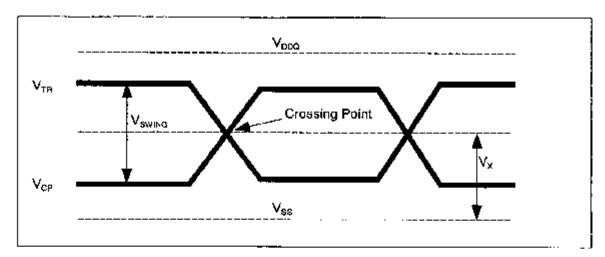

- 2.  $V_{\text{SWING}}$  (DC) specifies the input differential voltage  $|V_{\text{FR}}-V_{\text{CF}}|$  required for switching, where  $V_{\text{TR}}$  is the "true" input level and  $V_{\text{CF}}$  is the "complementary" input level.

Table 1.0-b Differential input AC logic levels

| Symbol              | Parameter                           | Min.                 | Max.                        | Units | Nates |

|---------------------|-------------------------------------|----------------------|-----------------------------|-------|-------|

| V <sub>SWING</sub>  | AC differential input voltage       | 0.70                 | $V_{\rm DOQ}$ =0.6          | V     | 1     |

| (AC)                |                                     |                      |                             |       |       |

| V <sub>x</sub> (AC) | AC differential cross point voltage | $0.5 \times V_{DDQ}$ | $0.5 \times V_{\text{DDQ}}$ | V     | 2     |

|                     |                                     | $=200 \mathrm{mV}$   | +200mV                      |       | :     |

#### <Notes>

- 1.  $V_{SWING}$  (AC) specifies the input differential voltage  $|V_{TR}-V_{CP}|$  required for switching, where  $V_{TR}$  is the "true" input signal and  $V_{CP}$  is the "complementary" input signal.

- The typical value of V<sub>x</sub> (AC) is expected to be about 0.5 × V<sub>poo</sub> of the transmitting device and V<sub>x</sub> (AC) is expected to track variations in V<sub>poo</sub>. Vx (AC) indicates the voltage at which differential input signals must be crossing.

Figure 1.0 SSTL\_2 differential input levels

#### 2.0 Differential Input AC test conditions

The differential AC test conditions are specified to be able to obtain reliable, reproducible test results in an automated test environment, where a relatively high noise environment makes it difficult to create clean signals with limited swing. The tester may therefore supply signals with a 1.5V peak to peak swing to drive the receiving device. Note however, that all timing specifications are still set relative to the differential AC input level. This is illustrated in Figure 2.0

| Symbol             | Parameter                                | Min.                  | Max.                         | Units | Notes |

|--------------------|------------------------------------------|-----------------------|------------------------------|-------|-------|

| Vr                 | Input timing measurement reference level | V <sub>X</sub> (cross | V <sub>X</sub> (cross point) |       | 1     |

| V <sub>SWING</sub> | Input signal peak to peak swing voltage  | -                     | 1.5                          | V     | 2     |

| SLEW               | Input signal slew rate                   | 1.0                   | _                            | V/ns  | 3     |

| t <sub>CKD</sub>   | Clock duty cycle                         | 45                    | 55                           | %     | 4     |

Table 2.0 Differential Input AC test conditions

#### <Notes>

- In all cases, input waveform timing is referenced to two input signals (V<sub>TR</sub> and V<sub>CP</sub>) crossing

point level (V<sub>X</sub>) applied to the device under test, where V<sub>TR</sub> is "true" input signal and V<sub>CP</sub> is the

"complementary" input signal. Table 1.0-b identifies the V<sub>X</sub> (AC) range supported in SSTL\_2

differential input.

- A 1.5V input pulse level is specified to allow consistent, repeatable test results in an automatic

test equipment (ATE) environment. Compliant devices must meet the V<sub>SWING</sub> (AC)

specification under actual use conditions. See Table 1.0-b.

- The 1V/ns input signal minimum slew rate is to be maintained the V<sub>II</sub>max (AC) to V<sub>II</sub>min (AC) range of the input signal swing, consistent with Table 2.2-b and Figure 2.3 of SSTL\_2 standard (EIAJ ED-5513).

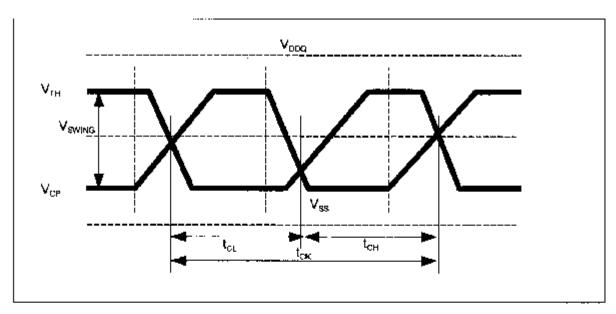

- 4. For periodic clock inputs, the duty cycle (t<sub>CKD</sub>) is defined to the t<sub>CH</sub> (or t<sub>CL</sub>) divided by t<sub>CK</sub> time when "true" input signal and "complementary" input signal are crossing each other.

See Figure 2.0-a.

This can be expressed by equation-1 or equation-2.

- $t_{CKD} = t_{CH} / t_{CK} \qquad (1)$

- $t_{CKD} = t_{CL} / t_{CK} \qquad (2)$

Figure 2.0 Differential AC input test signal wave form

#### 3.0 An example of SSTL\_2 Class I differential signals (Reference only)

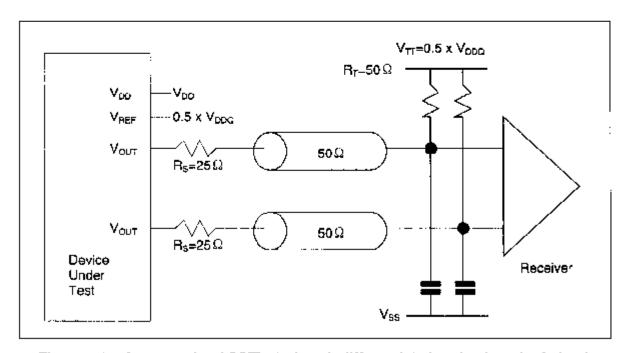

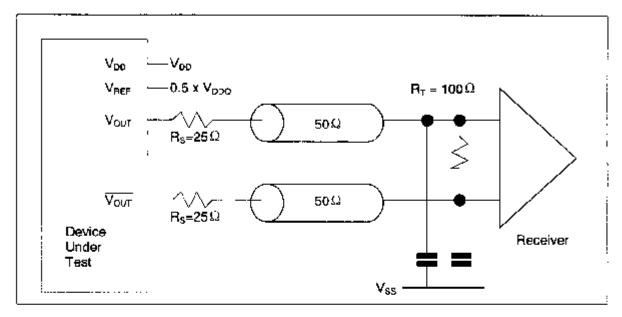

For reference only example, Figure 3.0 show the differential clocks are independently terminated by a  $50\Omega$  resistor. The value of  $I_{OR}$  (DC) and  $I_{OL}$  (DC) has to be abide by class-I specification.

Figure 3.0 An example of SSTL\_2 class I, differential signal using single load, and series resistor. (Reference only)

#### EIAJ ED-5515

Table 3.0 Viso specifications (Reference only)

| Symbol | Parameter                         | Min.                 | Max. | Units | Notes |

|--------|-----------------------------------|----------------------|------|-------|-------|

| Viso   | Input clock signal offset voltage | $0.5 \times V_{DDQ}$ |      | ν     | 1     |

| △Viso  | Viso variation                    | . —                  | +200 | mΫ    | 1     |

#### <Notes>

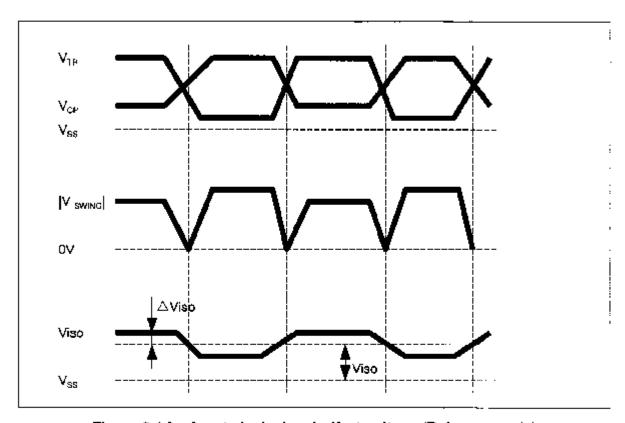

For only reference, the value of Viso is expected to be (|V<sub>TR</sub>+V<sub>CP</sub>|)/2 in case of each clock directly terminated by a 100Ω resistor, where V<sub>TR</sub> is the "true" input signal voltage and V<sub>CP</sub> is the "complementary" input signal voltage respectively.

See Figure 3.1-b.

Figure 3.1-b Input clock signal offset voltage (Reference only)

#### **EIAJ ED-5515**

#### 3.1 For reference only example of SSTL\_2 Class I differential clock signals

For reference only example, Figure 3.1-a show the differential clocks are directly terminated by a  $100\,\Omega$  resistor. The value of  $l_{OH}$  (DC),  $l_{OL}$  (DC) and Table-2.0 parameters have to be abide by class-I specification.

Figure 3.1-a An example of SSTL\_2 class I, differential signal using direct termination resister, and series resistor. (Reference only)

#### EXPLANATORY NOTES

#### 1. Objectives of Establishment

This standard defines differential input signal specification of SSTL\_2 (Stub Series Terminated Logic for 2.5V, hereafter "SSTL 2") which was previously established as EIAJ standard in August 1998. Using differential input signals, the standard aims to establish enough and superior noise margin for signal input signals to achieve devices on signal buses high frequency operation (More than 100–125MHz).

#### 2. Process of Discussion

In Memory Subcommittee (hereafter "the subcommittee"), there is an agreement between the subcommittee and IEDEC JC-16 committee (hereafter "JEDEC") that the subcommittee submits standard proposals to JEDEC when the subcommittee wants to establish EIAJ standard which may become a worldwide common standard. And after establishing a standard in JEDEC, the subcommittee standardizes it as EIAJ-JEDEC common standard.

Based on the agreement, SSTL\_2 proposal of EIAJ passed at JEDEC in December 1997. However, during more than 1 year long discussion about achieving high speed operation of devices, especially memory devices, were taken place in the industry. And, the industry considered superiority of differential input signal in discussion about interface for high frequency DRAMs such as DDR-SDRAM, SLDRAM.

To correspond to the consideration, the subcommittee started discussion about this standard in November 1997, and made first presentation at JEDEC meeting in December 1997. The proposal passed the JEDEC committee in June 1998. Then, the subcommittee made this standard as EJAJ standard.

This is an EIAJ and JEDEC joint standard.

#### **EIAJ ED-5515**

## 3. Members of Committee

This standard was discussed mainly by Memory Subcommittee on Semiconductor Standardization Committee/Integrated Circuit Group. The members are as shown below.

Semiconductor Standardization Committee>

Chairman

Mitsutoshi Ito

NEC Corp.

Semiconductor Standardization Committee/Integrated Circuit Group>

Chief Examiner

Motoo Nakano

Fujitsu Ltd.

<Memory Subcommittee>

Chief Examiner

Yoshiharu Nishiwaki

Oki Electric Industry Co., Ltd.

Vice-Chief Examiner

Mitsuo Higuchi

Fujitsu Ltd. LG Japan, Inc.

Member

Young Jun Roh

Oki Electric Industry Co., Ltd.

Shinya Takahashi Yeong-Il Kim

Hyundai Electronic Industry Japan, Inc.

Kenichi Kuramochi

Sanyo Electric Co., Inc.

Sharp Corp.

Yukichi Murakami Yasuhiko Takahashi

Nippon-Steel Semiconductor Inc.

Akira Uematsu

Seiko Epson Co.

Hitoshi Taniguchi

Sony Corp.

Toshio Kimura

Toshiba Corp.

Seijin Kim

Samsung Japan Ltd.

Soichiro Kamei

Texas Instruments Japan Ltd.

Masaharu Yajima

NEC corp.

Yasuhiro Suenaga

Nippon Motorola Ltd.

Atsushi Hiraishi

Hitachi Ltd.

Masao Ikushima

Matsushita Electric Industrial Co., Ltd.

Kazutami Arimoto

Mitsubishi Electric Corp.

Hidenori Hayashi

Rohm Ltd.

Special Member

Mitsuo Yasuhira

Matsushita Electronics Corp.

Miwa Monma

NEC Corp.

Yoshitomo Asakura

NEC Corp.